Datasheet Summary

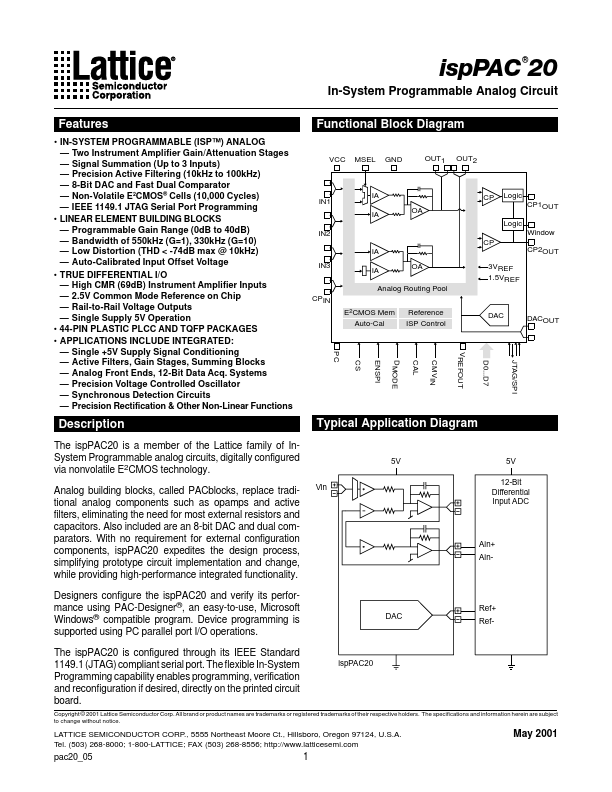

ispPAC ®20

In-System Programmable Analog Circuit

Features

- IN-SYSTEM PROGRAMMABLE (ISP™) ANALOG

- Two Instrument Amplifier Gain/Attenuation Stages

- Signal Summation (Up to 3 Inputs)

- Precision Active Filtering (10kHz to 100kHz)

- 8-Bit DAC and Fast Dual parator

- Non-Volatile E2CMOS® Cells (10,000 Cycles)

- IEEE 1149.1 JTAG Serial Port Programming

- LINEAR ELEMENT BUILDING BLOCKS

- Programmable Gain Range (0dB to 40dB)

- Bandwidth of 550kHz (G=1), 330kHz (G=10)

- Low Distortion (THD < -74dB max @ 10kHz)

- Auto-Calibrated Input Offset Voltage

- TRUE DIFFERENTIAL I/O

- High CMR (69dB) Instrument Amplifier Inputs

- 2.5V mon Mode Reference on Chip

- Rail-to-Rail Voltage Outputs

-...