Datasheet Summary

.. ispPAC30

In-System Programmable Analog Circuit

October 2002 Data Sheet

Features

- Flexible Interface and Programming Control

- -

- - Full configuration capability, SPI or JTAG modes Unlimited device updates using SRAM register E2CMOS® for non-volatile configuration storage Real-time microcontroller configuration/control High impedance: differential or single-ended 0V to 2.8V with programmable gains (±1 to ±10) Dual multiplexers (pin or serial port controlled) Connects easily to existing system circuits

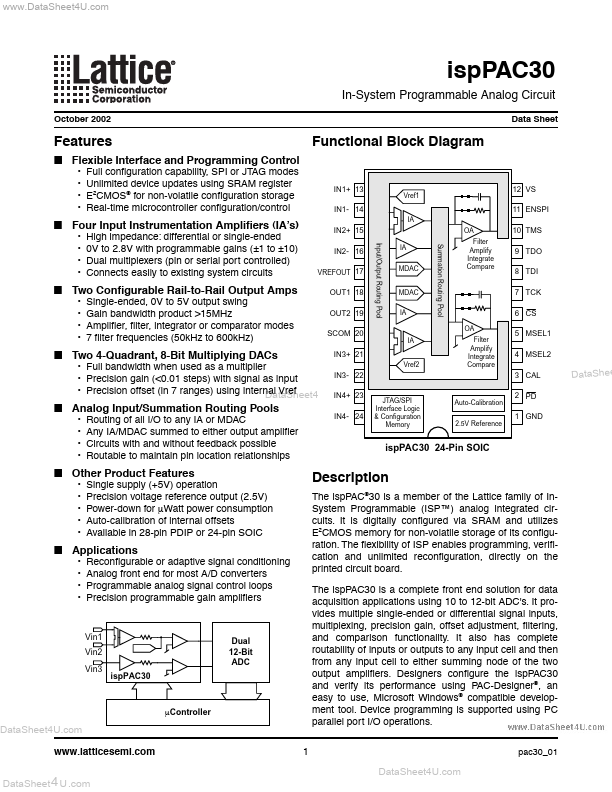

Functional Block Diagram

IN1+ 13

Vref1

12 VS 11 ENSPI

IA OA IA MDAC Filter Amplify Integrate pare

IN1- 14 IN2+ 15

Input/Output Routing Pool Summation Routing Pool

-...