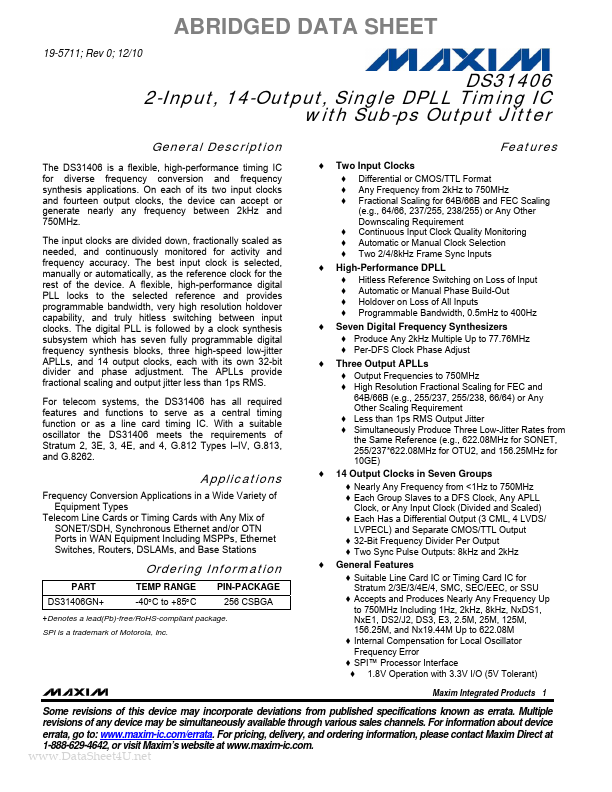

| Part | DS31406 |

|---|---|

| Description | Single DPLL Timing IC |

| Manufacturer | Maxim Integrated |

| Size | 149.94 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MT6835 | MagnTek | 21-Bit High Accuracy Magnetic Angle Encoder IC |

| LTH7R | FINE MADE ELECTRONICS | Charger management IC |

| EG1000AE | Yige | linear constant current IC |