MAX3877 Overview

Key Specifications

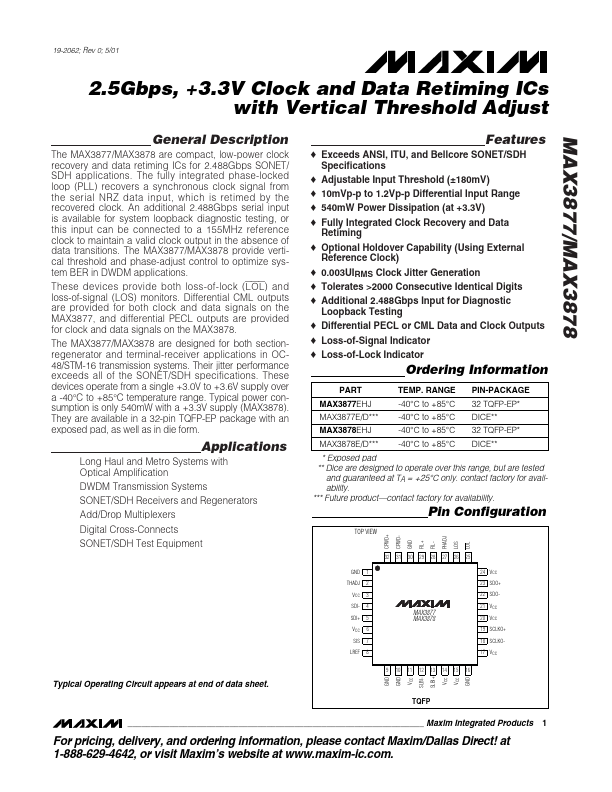

Package: TQFP

Pins: 32

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

The MAX3877/MAX3878 are compact, low-power clock recovery and data retiming ICs for 2.488Gbps SONET/ SDH applications. The fully integrated phase-locked loop (PLL) recovers a synchronous clock signal from the serial NRZ data input, which is retimed by the recovered clock.