| Part | MAX9320B |

|---|---|

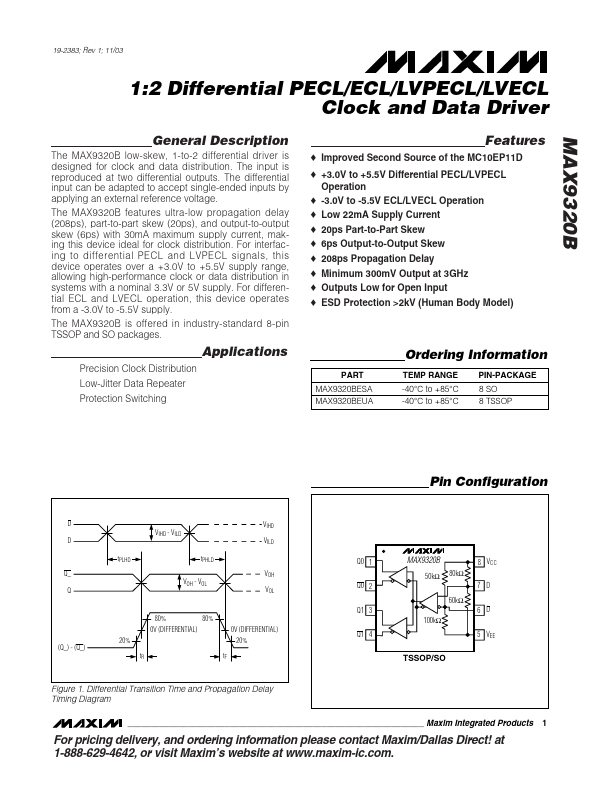

| Description | 1:2 Differential PECL/ECL/LVPECL/LVECL Clock and Data Driver |

| Manufacturer | Maxim Integrated |

| Size | 120.43 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MAX9321A | Maxim Integrated | Differential LVPECL/LVECL/HSTL Receiver/Drivers |