SY100S360

SY100S360 is Dual Parity Checker/generator manufactured by Micrel Semiconductor.

Micrel, Inc.

DUAL PARITY CHECKER/ GENERATOR

Features

DESCRIPTION s Max. propagation delay of 2200ps s IEE min. of

- 70m A s Industry standard 100K ECL levels s Extended supply voltage option:

VEE =

- 4.2V to

- 5.5V s Voltage and temperature pensation for improved noise immunity s Internal 75kΩ input pull-down resistors s 15% faster than Fairchild 300K s Approximately 30% lower power than Fairchild 300K s Function and pinout patible with Fairchild F100K s Available in 28-pin PLCC package

The SY100S360 is a dual parity checker/generator and is designed for use in high-performance ECL systems. The inputs are segmented into two groups of nine inputs each and the parity output is at a logic LOW when an even number of inputs are at a logic HIGH. In each group, one of the nine inputs (Ia, Ib) has a shorter propagation delay and, therefore, is ideal as the expansion input for parity generation of wider data.

A pare output (C) is also provided which allows parison of two 8-bit words. A logic LOW on the C output indicates a match. The inputs on this device have 75kΩ pull-down resistors.

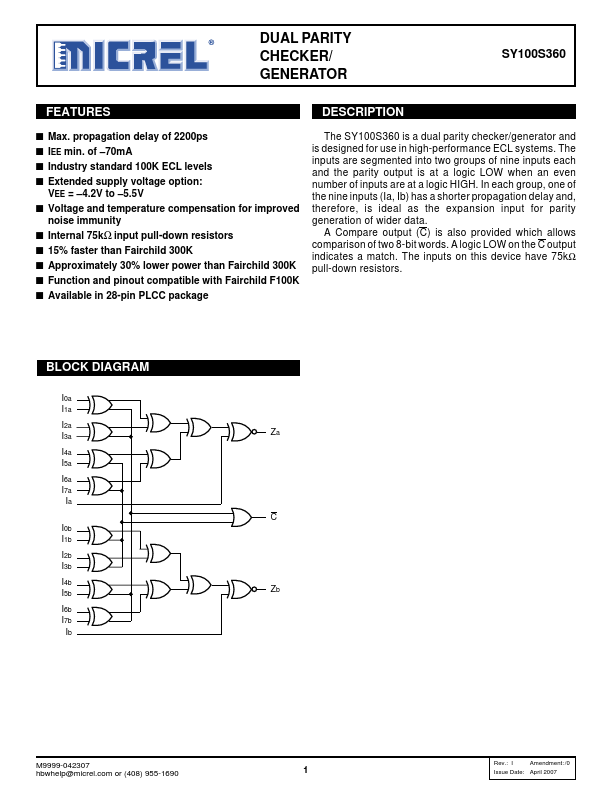

BLOCK DIAGRAM

I0a I1a

I2a I3a

I4a I5a

I6a I7a Ia

I0b I1b

I2b I3b

I4b I5b

I6b I7b Ib

Za C Zb

M9999-042307 hbwhelp@micrel. or (408) 955-1690

Rev.: I

Amendment: /0

Issue Date: April 2007

Micrel, Inc.

PACKAGE/ORDERING INFORMATION

Ordering Information

I5a I4a I3a VEES I2a I1a I0a

Package Operating

Package...