SY89808L

SY89808L is 1:9 DIFFERENTIAL HSTL (1.5V) FANOUT BUFFER/TRANSLATOR manufactured by Micrel Semiconductor.

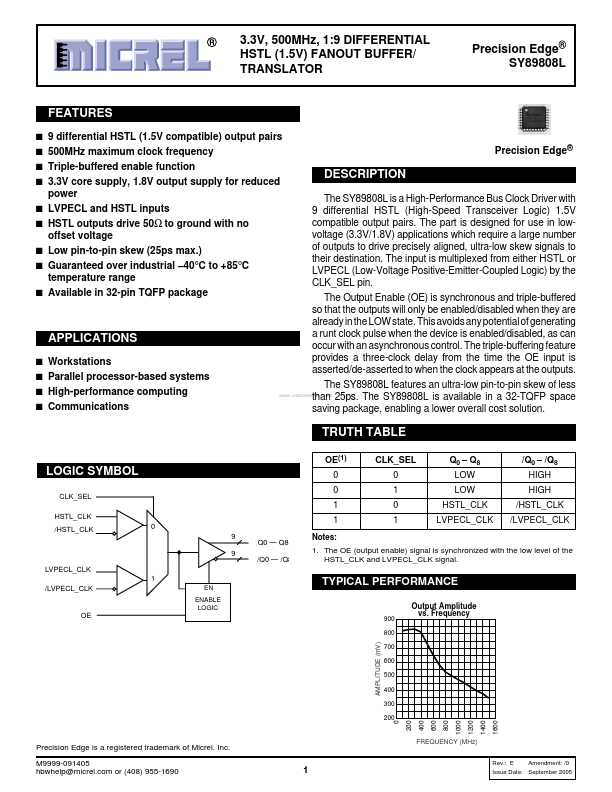

FEATURES s 9 differential HSTL (1.5V patible) output pairs s 500MHz maximum clock frequency s Triple-buffered enable function s 3.3V core supply, 1.8V output supply for reduced s s s s s

Precision Edge®

DESCRIPTION power LVPECL and HSTL inputs HSTL outputs drive 50Ω to ground with no offset voltage Low pin-to-pin skew (25ps max.) Guaranteed over industrial

- 40°C to +85°C temperature range Available in 32-pin TQFP package

APPLICATIONS s Workstations s Parallel processor-based systems s High-performance puting s munications

The SY89808L is a High-Performance Bus Clock Driver with 9 differential HSTL (High-Speed Transceiver Logic) 1.5V patible output pairs. The part is designed for use in lowvoltage (3.3V/1.8V) applications which require a large number of outputs to drive precisely aligned, ultra-low skew signals to their destination. The input is multiplexed from either HSTL or LVPECL (Low-Voltage Positive-Emitter-Coupled Logic) by the CLK_SEL pin. The Output Enable (OE) is synchronous and triple-buffered so that the outputs will only be enabled/disabled when they are already in the LOW state. This avoids any potential of generating a runt clock pulse when the device is enabled/disabled, as can occur with an asynchronous control. The triple-buffering feature provides a three-clock delay from the time the OE input is asserted/de-asserted to when the clock appears at the outputs. The SY89808L features an ultra-low pin-to-pin skew of less .. than 25ps. The SY89808L is available in a 32-TQFP space saving package, enabling a lower overall cost solution.

TRUTH TABLE

OE(1) CLK_SEL 0 1 0 1

LOGIC SYMBOL

CLK_SEL HSTL_CLK /HSTL_CLK 0 9 9 LVPECL_CLK 1 /LVPECL_CLK

EN ENABLE LOGIC

Q0

- Q8 LOW LOW HSTL_CLK LVPECL_CLK

/Q0

- /Q8 HIGH HIGH /HSTL_CLK /LVPECL_CLK

0 0 1 1

Q0

- Q8 /Q0

- /Q8

Notes: 1. The OE (output enable) signal is synchronized with the low level of the HSTL_CLK and LVPECL_CLK signal.

TYPICAL PERFORMANCE

Output Amplitude vs. Frequency

900 800

AMPLITUDE...