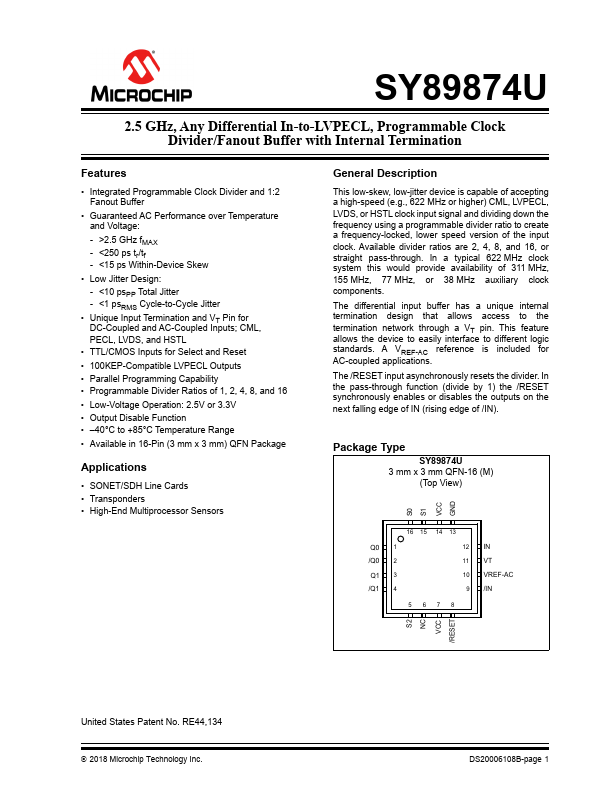

SY89874U Overview

Description

This low-skew, low-jitter device is capable of accepting a high-speed (e.g., 622 MHz or higher) CML, LVPECL, LVDS, or HSTL clock input signal and dividing down the frequency using a programmable divider ratio to create a frequency-locked, lower speed version of the input clock. Available divider ratios are 2, 4, 8, and 16, or straight pass-through.

Key Features

- Integrated Programmable Clock Divider and 1:2 Fanout Buffer

- Guaranteed AC Performance over Temperature and Voltage

- >2.5 GHz fMAX

- <250 ps tr/tf

- <15 ps Within-Device Skew

- Low Jitter Design

- <10 psPP Total Jitter

- <1 psRMS Cycle-to-Cycle Jitter

- Unique Input Termination and VT Pin for DC-Coupled and AC-Coupled Inputs; CML, PECL, LVDS, and HSTL

- TTL/CMOS Inputs for Select and Reset