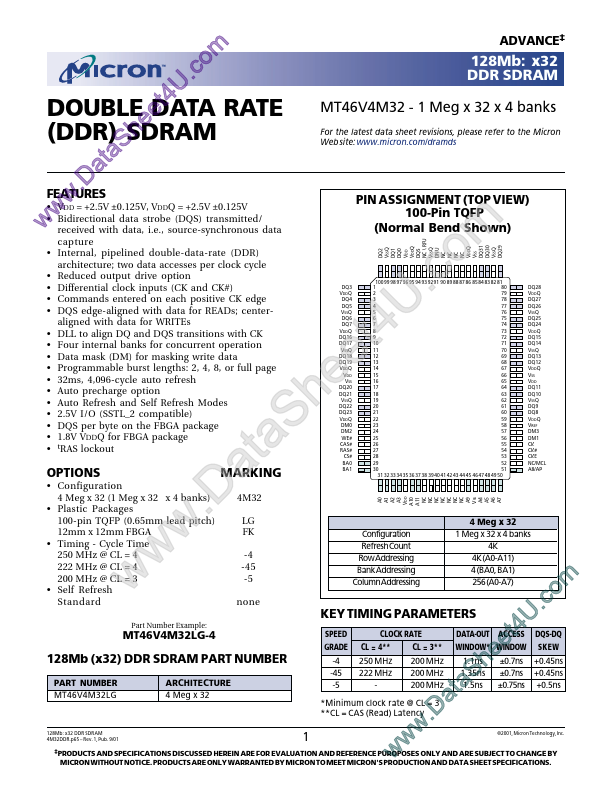

MT46V4M32

MT46V4M32 is DOUBLE DATA RATE DDR SDRAM manufactured by Micron Technology.

m o .c U 4 DOUBLE eDATA RATE et h (DDR) S SDRAM a t a D . Features w w w

- VDD = +2.5V ±0.125V, VDDQ = +2.5V ±0.125V

- Bidirectional data strobe (DQS) transmitted/ received with data, i.e., source-synchronous data capture

- Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

- Reduced output drive option

- Differential clock inputs (CK and CK#)

- mands entered on each positive CK edge

- DQS edge-aligned with data for READs; centeraligned with data for WRITEs

- DLL to align DQ and DQS transitions with CK

- Four internal banks for concurrent operation

- Data mask (DM) for masking write data

- Programmable burst lengths: 2, 4, 8, or full page

- 32ms,...