MT4LC4M16R6

Description

The 4 Meg x 16 DRAM is a high-speed CMOS, dynamic random-access memory device containing 67,108,864 bits and designed to operate from 3V to 3.6V.

Key Features

- Single +3.3V ±0.3V power supply

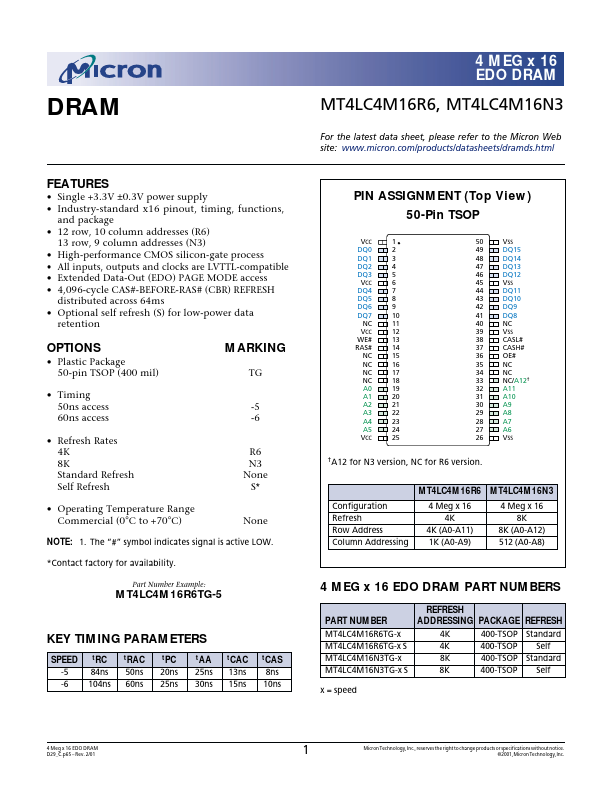

- Industry-standard x16 pinout, timing, functions, and package

- High-performance CMOS silicon-gate process

- Extended Data-Out (EDO) PAGE MODE access

- 4,096-cycle CAS#-BEFORE-RAS# (CBR) REFRESH distributed across 64ms

- Optional self refresh (S) for low-power data retention

- Plastic Package 50-pin TSOP (400 mil)

- Timing 50ns access 60ns access

- Refresh Rates 4K 8K Standard Refresh Self Refresh

- Operating Temperature Range mercial (0°C to +70°C)