MT9041 Overview

Description

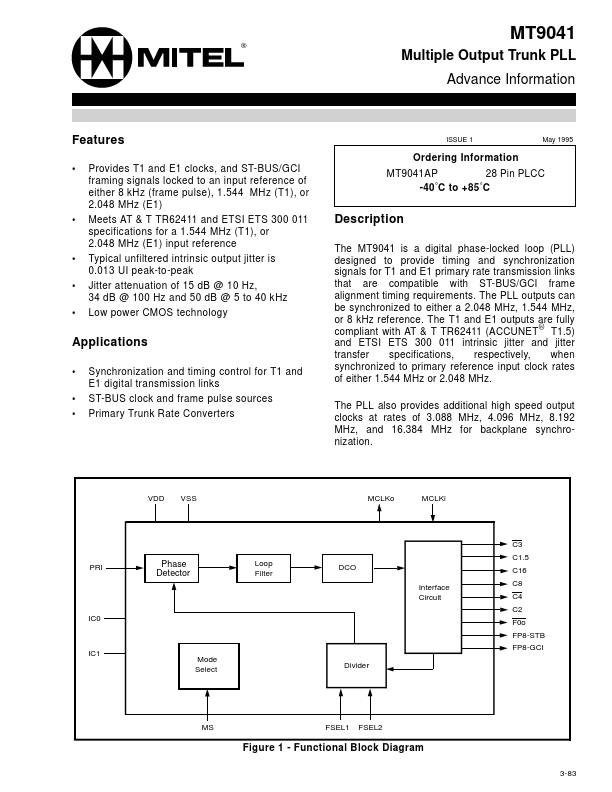

The MT9041 is a digital phase-locked loop (PLL) designed to provide timing and synchronization signals for T1 and E1 primary rate transmission links that are compatible with ST-BUS/GCI frame alignment timing requirements. The PLL outputs can be synchronized to either a 2.048 MHz, 1.544 MHz, or 8 kHz reference.