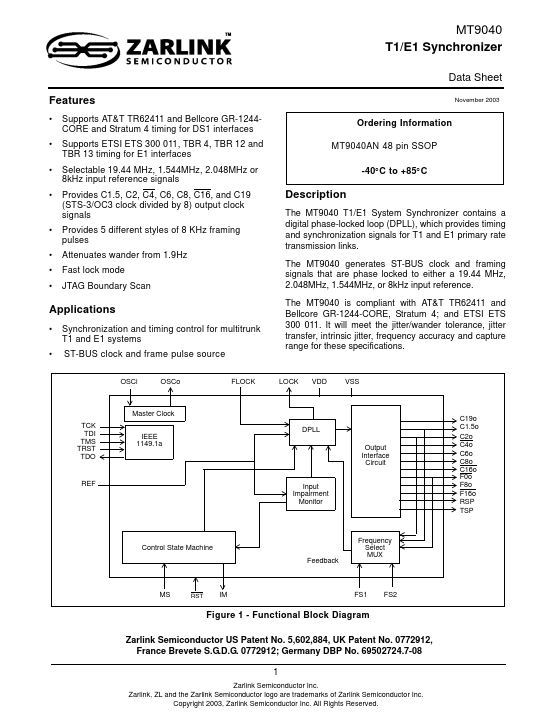

| Part | MT9040 |

|---|---|

| Description | T1/E1 Synchronizer |

| Manufacturer | Zarlink Semiconductor |

| Size | 424.10 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MT9042 | Mitel Networks Corporation | Global Digital Trunk Synchronizer |

| MT9041 | Mitel Networks Corporation | Multiple Output Trunk PLL |

| MT9044 | Mitel Networks Corporation | T1/E1/OC3 System Synchronizer |

| MT9041B | Mitel Networks Corporation | T1/E1 System Synchronizer |

| MT9042C | Mitel Networks Corporation | Multitrunk System Synchronizer |