M2V12D20TP

M2V12D20TP is 512M Double Data Rate Synchronous DRAM manufactured by Mitsubishi Electric.

- Part of the M2V comparator family.

- Part of the M2V comparator family.

DESCRIPTION

M2S12D20TP is a 4-bank x 33,554,432-word x 4-bit, M2S12D30TP is a 4-bank x 16,777,216-word x 8-bit, double data rate synchronous DRAM, with SSTL_2 interface. All control and address signals are referenced to the rising edge of CLK. Input data is registered on both edges of data strobes, and output data and data strobe are referenced on both edges of CLK. The M2S12D20/30TP achieve very high speed data rate up to 133MHz, and are suitable for main memory in puter systems.

FEATURES

- Vdd=Vddq=2.5V+0.2V

- Double data rate architecture; two data transfers per clock cycle

- Bidirectional, data strobe (DQS) is transmitted/received with data

- Differential clock inputs (CLK and /CLK)

- DLL aligns DQ and DQS transitions

- mands are entered on each positive CLK edge;

- data and data mask are referenced to both edges of DQS

- 4 bank operations are controlled by BA0, BA1 (Bank Address)

- /CAS latency- 2.0/2.5 (programmable)

- Burst length- 2/4/8 (programmable)

- Burst type- sequential / interleave (programmable)

- Auto precharge / All bank precharge is controlled by A10

- 8192 refresh cycles /64ms (4 banks concurrent refresh)

- Auto refresh and Self refresh

- Row address A0-12 / Column address A0-9,11-12(x4)/ A0-9,11(x8) SSTL_2 Interface

- 400-mil, 66-pin Thin Small Outline Package (TSOP II)

- JEDEC standard

- Low Power for the Self Refresh Current ICC6 :4m A (-75L,-10L)

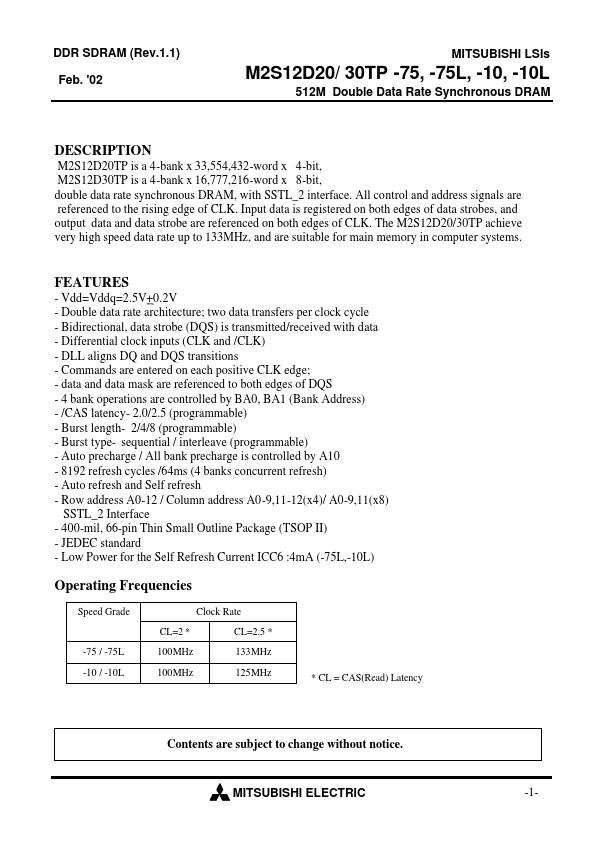

Operating Frequencies

Speed Grade CL=2

- -75 / -75L -10 / -10L 100MHz 100MHz Clock Rate CL=2.5

- 133MHz 125MHz

- CL = CAS(Read) Latency

Contents are subject to change without notice.

MITSUBISHI ELECTRIC

-1-

DDR SDRAM (Rev.1.1) Feb.ELECTRIC '02

MITSUBISHI

MITSUBISHI LSIs

M2S12D20/ 30TP -75, -75L, -10, -10L

512M Double Data Rate Synchronous DRAM PIN CONFIGURATION(TOP VIEW) x4 x8

VDD NC VDDQ NC DQ0 VSSQ NC NC VDDQ NC DQ1 VSSQ NC NC VDDQ NC NC VDD NC NC /WE /CAS /RAS /CS NC BA0 BA1 A10/AP A0 A1 A2 A3 VDD VDD DQ0 VDDQ NC DQ1 VSSQ NC DQ2 VDDQ NC DQ3 VSSQ NC NC VDDQ NC NC VDD NC NC /WE /CAS /RAS...