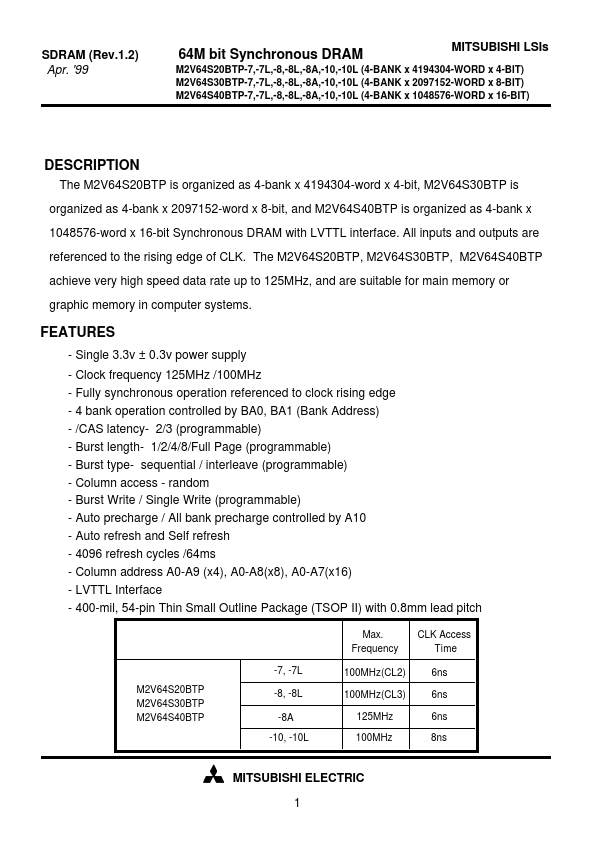

M2V64S20BTP-7 Key Features

- Single 3.3v ± 0.3v power supply

- Clock frequency 125MHz /100MHz

- Fully synchronous operation referenced to clock rising edge

- 4 bank operation controlled by BA0, BA1 (Bank Address)

- /CAS latency- 2/3 (programmable)

- Burst length- 1/2/4/8/Full Page (programmable)

- Burst type- sequential / interleave (programmable)

- Column access

- random

- Burst Write / Single Write (programmable)