M5M4V16169DRT-15

M5M4V16169DRT-15 is 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM manufactured by Mitsubishi Electric.

MITSUBISHI LSIs

M5M4V16169DTP/RT-7,-8,-10,-15

16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

Preliminary

This document is a preliminary Target Spec. and some of the contents are subject to change without notice.

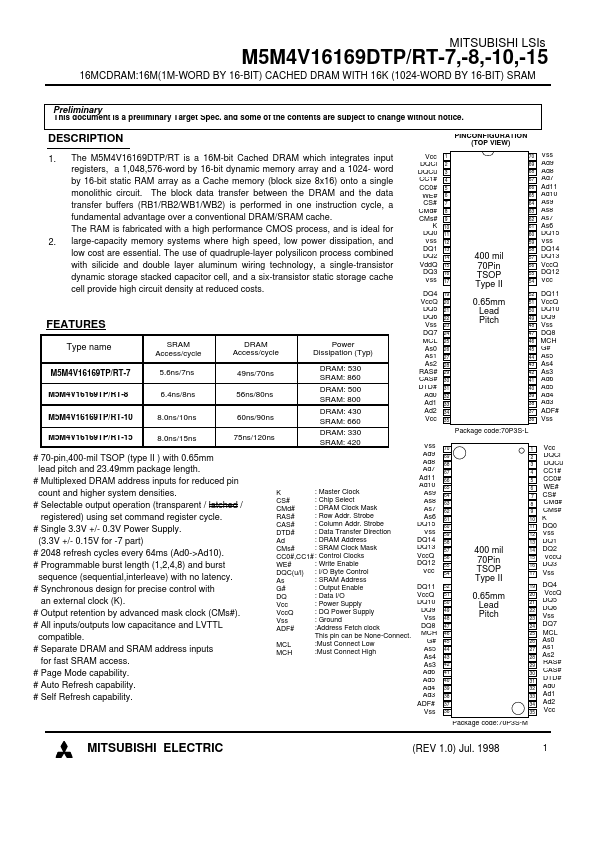

PINCONFIGURATION (TOP VIEW) Vcc DQCl DQCu CC1# CC0# WE# CS# CMd# CMs# K DQ0 Vss DQ1 DQ2 VddQ DQ3 Vss DQ4 VccQ DQ5 DQ6 Vss DQ7 MCL As0 As1 As2 RAS# CAS# DTD# Ad0 Ad1 Ad2 Vcc

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 70 69 68 67 66 65 64 63 62 61 60 59 58

DESCRIPTION

1. The M5M4V16169DTP/RT is a 16M-bit Cached DRAM which integrates input registers, a 1,048,576-word by 16-bit dynamic memory array and...