M5M4V16G50DFP-10

M5M4V16G50DFP-10 is 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM manufactured by Mitsubishi Electric.

SGRAM (Rev. 0.0) Jan'97 Preliminary

MITSUBISHI LSIs

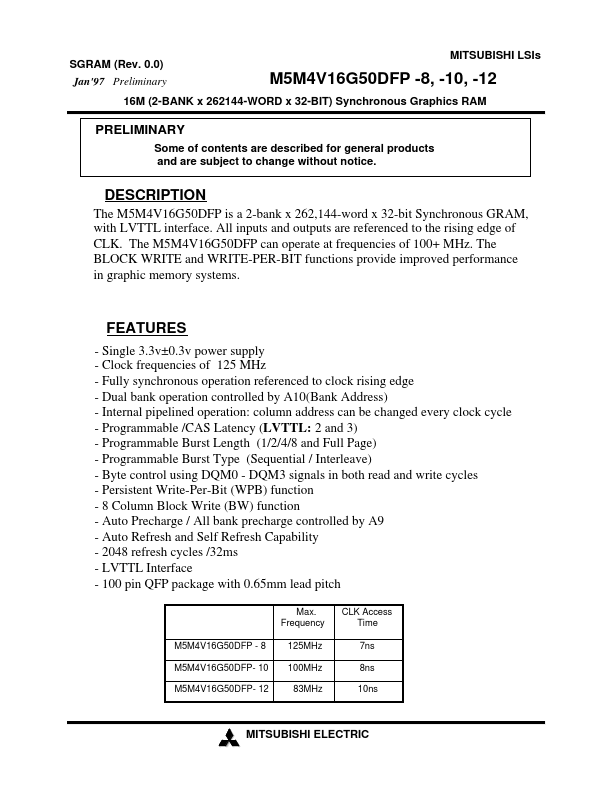

M5M4V16G50DFP -8, -10, -12

16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM

PRELIMINARY

Some of contents are described for general products and are subject to change without notice.

DESCRIPTION

The M5M4V16G50DFP is a 2-bank x 262,144-word x 32-bit Synchronous GRAM, with LVTTL interface. All inputs and outputs are referenced to the rising edge of CLK. The M5M4V16G50DFP can operate at frequencies of 100+ MHz. The BLOCK WRITE and WRITE-PER-BIT functions provide improved performance in graphic memory systems.

Features

- Single 3.3v±0.3v power supply

- Clock frequencies of 125 MHz

- Fully synchronous operation referenced to...