M5M4V64S20ATP-8

M5M4V64S20ATP-8 is 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM manufactured by Mitsubishi Electric.

- Part of the M5M comparator family.

- Part of the M5M comparator family.

SDRAM (Rev.0.2) Jan'97 Preliminary

MITSUBISHI LSIs

M5M4V64S20ATP-8, -10, -12

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM

PRELIMINARY

Some of contents are subject to change without notice.

DESCRIPTION

The M5M4V64S20ATP is a 4-bank x 4194304-word x 4-bit Synchronous DRAM, with LVTTL interface. All inputs and outputs are referenced to the rising edge of CLK. The M5M4V64S20ATP achieves very high speed data rate up to 125MHz, and is suitable for main memory or graphic memory in puter systems.

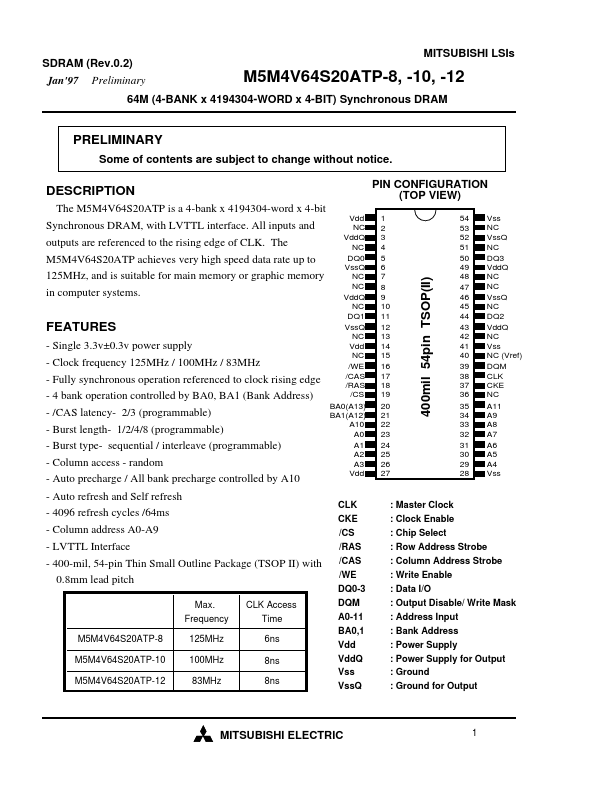

Vdd NC VddQ NC DQ0 VssQ NC NC VddQ NC DQ1 VssQ NC Vdd NC /WE /CAS /RAS /CS BA0(A13) BA1(A12) A10 A0 A1 A2 A3 Vdd

PIN CONFIGURATION (TOP VIEW)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18...