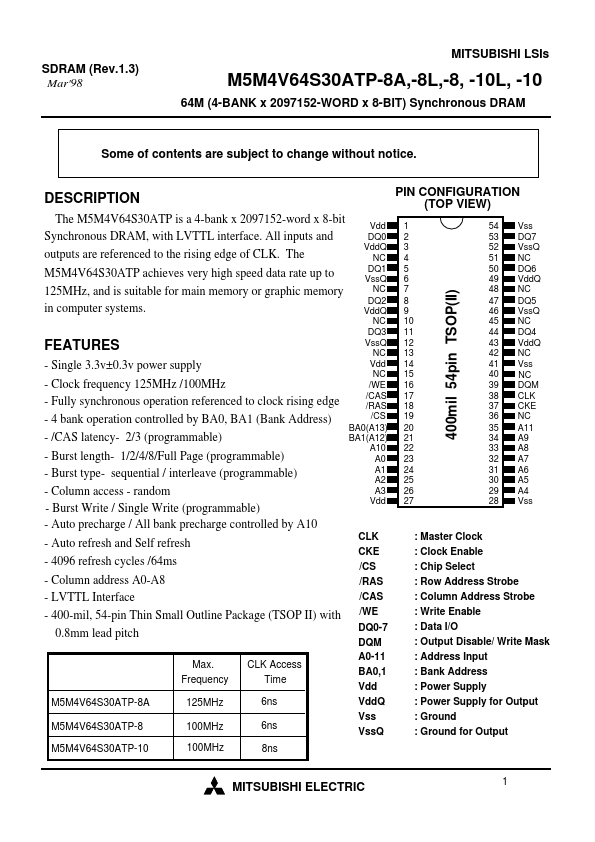

M5M4V64S30ATP-8A

Description

The M5M4V64S30ATP is a 4-bank x 2097152-word x 8-bit Synchronous DRAM, with LVTTL interface.

Key Features

- Clock Enable: CKE controls internal clock

- When CKE is low, internal clock for the following cycle is ceased

- CKE is also used to select auto / self refresh

- After self refresh mode is started, CKE bees asynchronous input

- Self refresh is maintained as long as CKE is low

- Chip Select: When /CS is high, any mand means No Operation

- bination of /RAS, /CAS, /WE defines basic mands

- A0-11 specify the Row / Column Address in conjunction with BA0,1

- The Row Address is specified by A0-11

- A10 is also used to indicate precharge option