M5M5Y5672TG-22

M5M5Y5672TG-22 is 18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM manufactured by Mitsubishi Electric.

DESCRIPTION

The M5M5Y5672TG is a family of 18M bit synchronous SRAMs organized as 262144-words by 72-bit. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Mitsubishi's SRAMs are fabricated with high performance, low power CMOS technology, providing greater reliability. M5M5Y5672TG operates on a single 1.8V power supply and are 1.8V CMOS patible.

FEATURES

- Fully registered inputs and outputs for pipelined operation

- Fast clock speed: 250, 225, and 200 MHz

- Fast access time: 2.6, 2.8, 3.2 ns

- Single 1.8V +150/-100m V power supply VDD

- Separate VDDQ for 1.8V I/O

- Individual byte write (BWa#

- BWh#) controls may be tied LOW

- Single Read/Write control pin (W#)

- Echo Clock outputs track data output drivers

- ZQ mode pin for user-selectable output drive strength

- 2 User programmable chip enable inputs for easy depth expansion

- Linear or Interleaved Burst Modes

- JTAG boundary scan support

APPLICATION

High-end networking products that require high bandwidth, such as switches and routers.

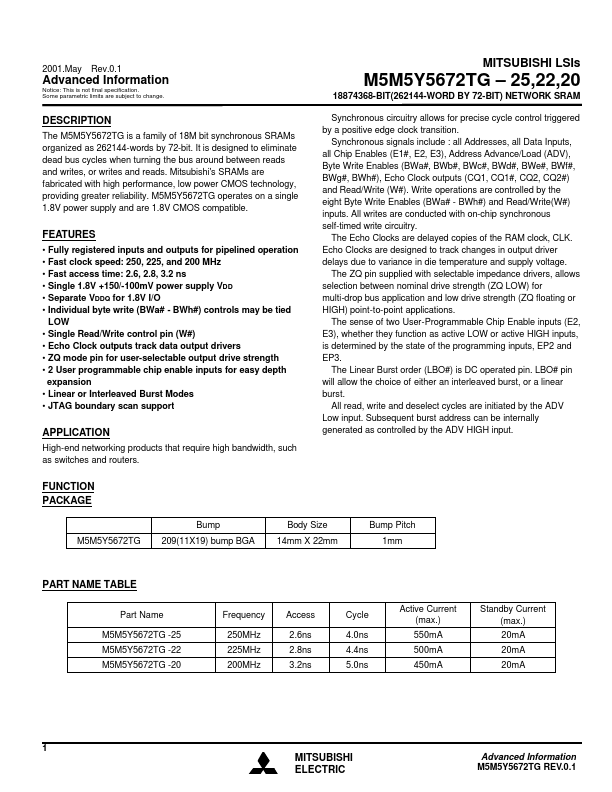

FUNCTION PACKAGE

Bump M5M5Y5672TG 209(11X19) bump BGA Body Size 14mm X 22mm Bump Pitch 1mm

PART NAME TABLE

Part Name M5M5Y5672TG -25 M5M5Y5672TG -22 M5M5Y5672TG -20 Frequency 250MHz 225MHz 200MHz Access 2.6ns 2.8ns 3.2ns Cycle 4.0ns 4.4ns 5.0ns Active Current (max.) 550m A 500m A...