V58C2256

V58C2256 is HIGH PERFORMANCE 2.5 VOLT 256 Mbit DDR SDRAM manufactured by Mosel Vitelic Corp.

Features

- High speed data transfer rates with system frequency up to 166 MHz

- Data Mask for Write Control

- Four Banks controlled by BA0 & BA1

- Programmable CAS Latency: 2, 2.5

- Programmable Wrap Sequence: Sequential or Interleave

- Programmable Burst Length: 2, 4, 8 for Sequential Type 2, 4, 8 for Interleave Type

- Automatic and Controlled Precharge mand

- Power Down Mode

- Auto Refresh and Self Refresh

- Refresh Interval: 8192 cycles/64 ms

- Available in 66-pin 400 mil TSOP or 60 Ball SOC BGA

- SSTL-2 patible I/Os

- Double Data Rate (DDR)

- Bidirectional Data Strobe (DQS) for input and output data, active on both edges

- On-Chip DLL aligns DQ and DQs transitions with CK transitions

- Differential clock inputs CK and CK

- Power Supply 2.5V ± 0.2V

- QFC options for FET control. x4 parts.

- Note: DDR 333B Supports PC2700 module with 2.5-3-3 timing DDR 266A Supports PC2100 module with 2-2-2 timing DDR 266B Supports PC2100 module with 2.5-3-3 timing DDR 200 Supports PC1600 module with 2-2-2 timing

Description

The V58C2256(804/404/164)S is a four bank DDR DRAM organized as 4 banks x 8Mbit x 8 (804), 4 banks x 4Mbit x 16 (164), or 4 banks x 16Mbit x 4 (404). The V58C2256(804/404/164)S achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock. All of the control, address, circuits are synchronized with the positive edge of an externally supplied clock. I/O transactions are ocurring on both edges of DQS. Operating the four memory banks in an interleaved fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate is possible depending on burst length, CAS latency and speed grade of the device.

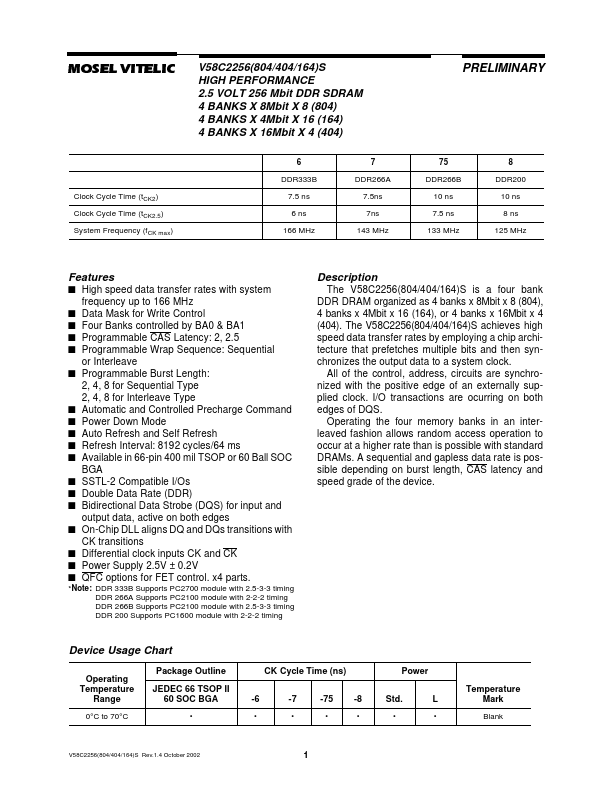

Device Usage Chart

Operating Temperature Range

0°C to 70°C

Package Outline JEDEC 66 TSOP II 60 SOC BGA

- CK Cycle Time (ns) -6

- Power -8

- -7

- -75

- Std.

- L

- Temperature Mark

Blank

V58C2256(...