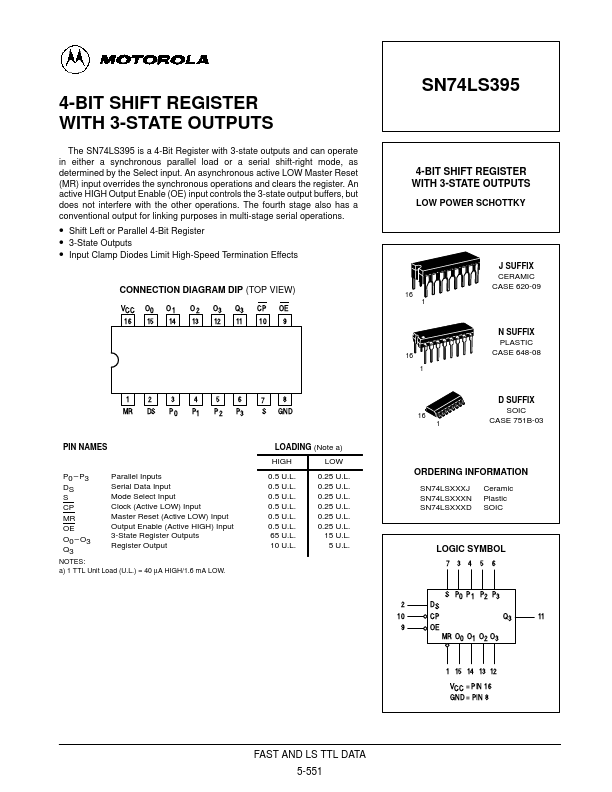

| Part | 74LS395 |

|---|---|

| Description | 4-BIT SHIFT REGISTER |

| Manufacturer | Motorola Semiconductor |

| Size | 196.62 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74LS393 | Fairchild Semiconductor | Dual 4-Bit Binary Counter |

| 74LS393 | Hitachi Semiconductor | DUAL 4-BIT BINARY COUNTERS |

| 74LS390 | Fairchild Semiconductor | Dual 4-Bit Decade Counter |

| 74LS399 | Texas Instruments | QUADRUPLE 2-INPUT MULTIPLEXER |