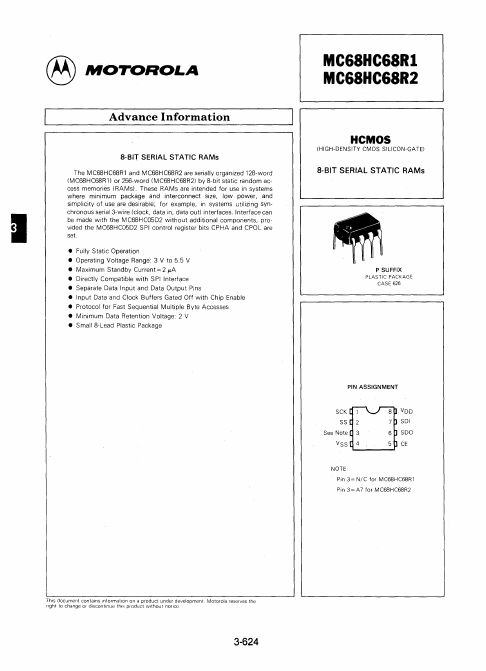

- Part: MC68HC68R2

- Manufacturer: Motorola Semiconductor

- Size: 81.25 KB

Related Motorola Semiconductor Datasheets

| Part Number | Description |

|---|---|

| MC68HC68R1 | 8-BIT SERIAL STATIC RAMs |

| MC68HC68T1 | Straight 1-Row BergStik II Headers |

| MC68HC000 | Low Power HCMOS 16-/32-Bit Microprocessor |

| MC68HC04J2 | 8-Bit Microcontroller |

| MC68HC04J3 | 8-Bit Microcontroller |