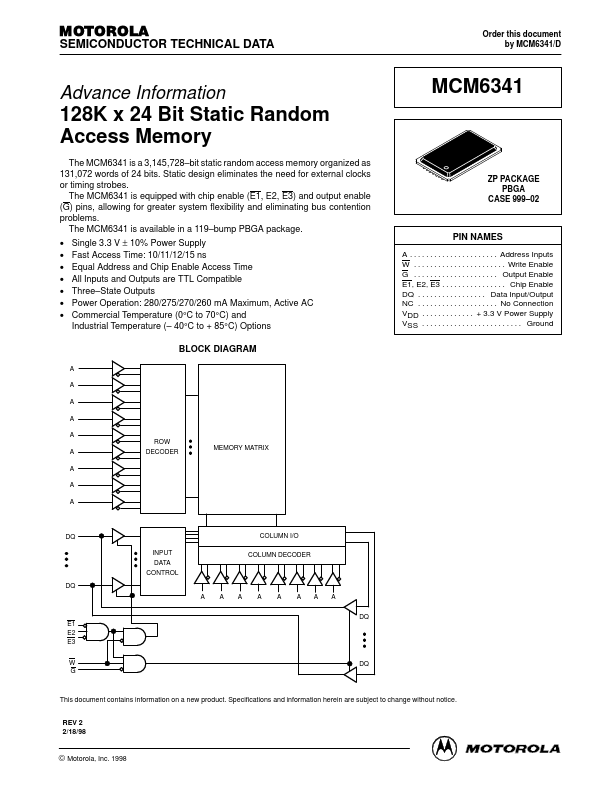

MCM6341 Description

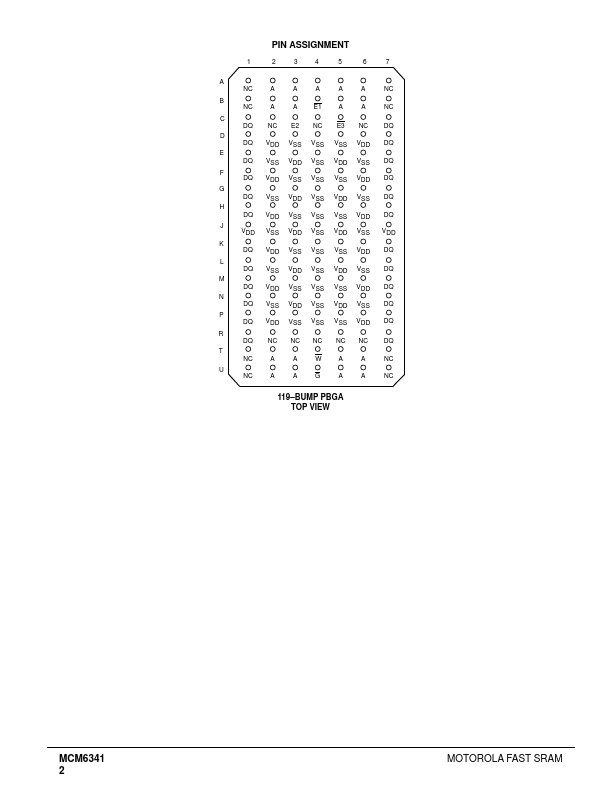

Static design eliminates the need for external clocks or timing strobes. The MCM6341 is equipped with chip enable (E1, E2, E3) and output enable (G) pins, allowing for greater system flexibility and eliminating bus contention problems. The MCM6341 is available in a 119 bump PBGA package.