MCM64AF32 Overview

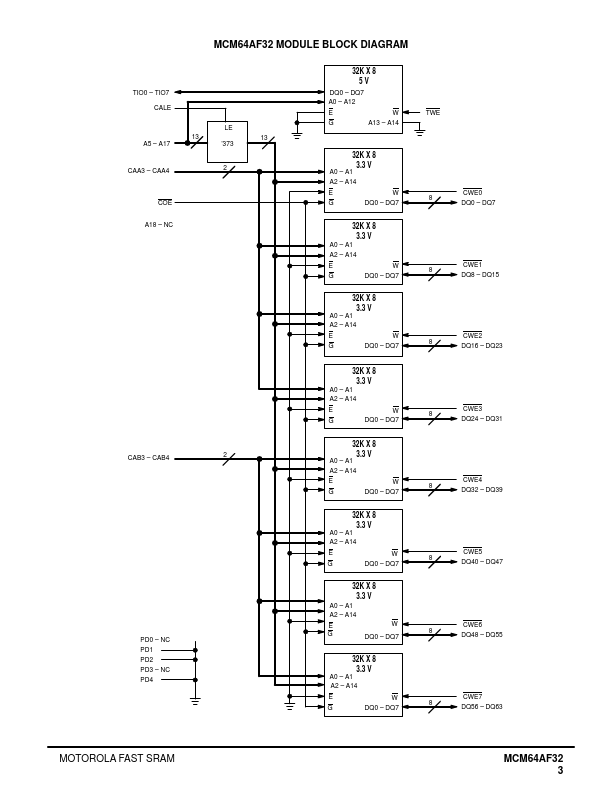

The module is configured as 32K x 64 bits in a 160 pin card edge connector. The module uses eight Motorola 3.3 V 32K x 8 FSRAMs for the cache memory, one Motorola 5 V 32K x 8 FSRAM for the tag RAM, and an upper order address latch. Eight write enables are provided for byte write control.