Datasheet Summary

MOTOROLA

Freescale Semiconductor, Inc.

SEMICONDUCTOR TECHNICAL DATA

Order Number: MPC93R51/D Rev 0, 12/2002

Low Voltage PLL Clock Driver

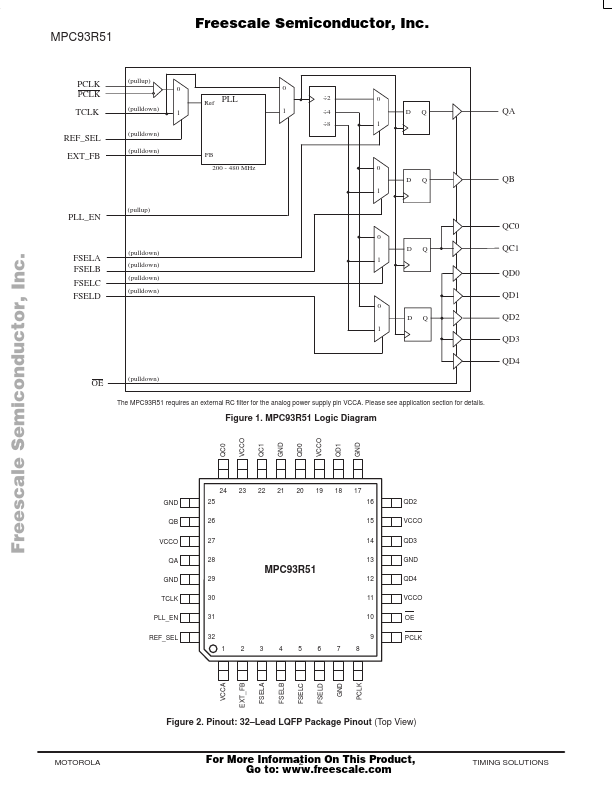

The MPC93R51 is a 3.3V patible, PLL based clock generator targeted for high performance clock distribution systems. With output frequencies of up to 240 MHz and a maximum output skew of 150 ps the MPC93R51 is an ideal solution for the most demanding clock tree designs. The device offers 9 low skew clock outputs, each is configurable to support the clocking needs of the various high-performance microprocessors including the PowerQuicc II integrated munication microprocessor. The devices employs a fully differential PLL design to minimize...