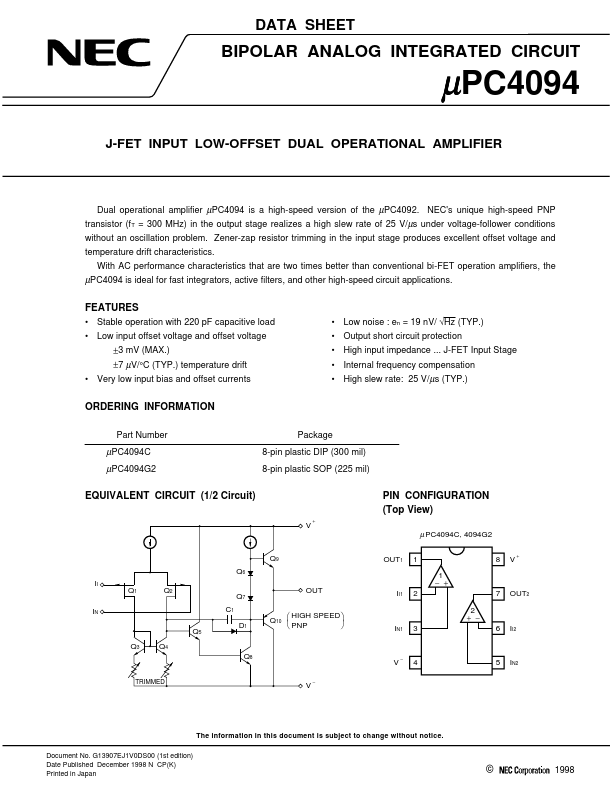

UPC4094 Key Features

- Stable operation with 220 pF capacitive load

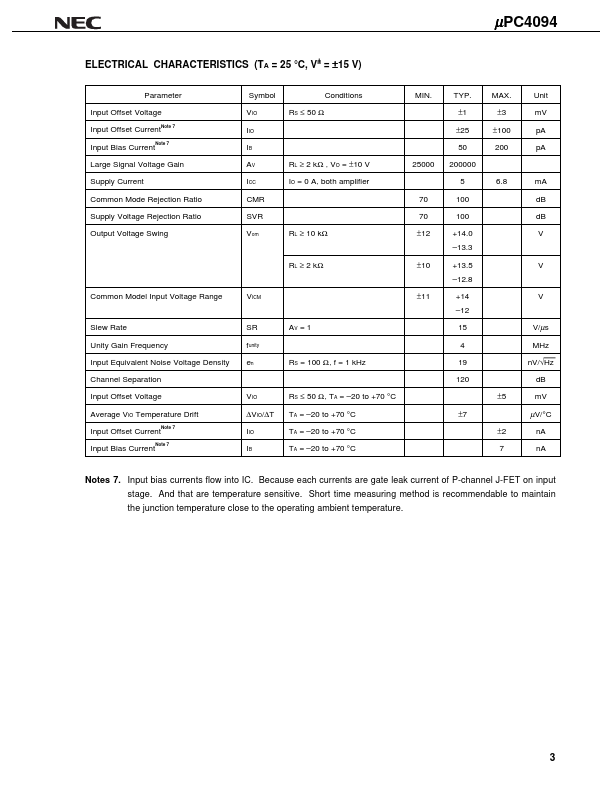

- Low input offset voltage and offset voltage ±3 mV (MAX.) ±7 µV/°C (TYP.) temperature drift

- Very low input bias and offset currents

- Low noise : en = 19 nV/ √Hz (TYP.)

- Output short circuit protection

- High input impedance ... J-FET Input Stage

- Internal frequency pensation

- High slew rate: 25 V/µs (TYP.)