UPD4481322 Overview

Description

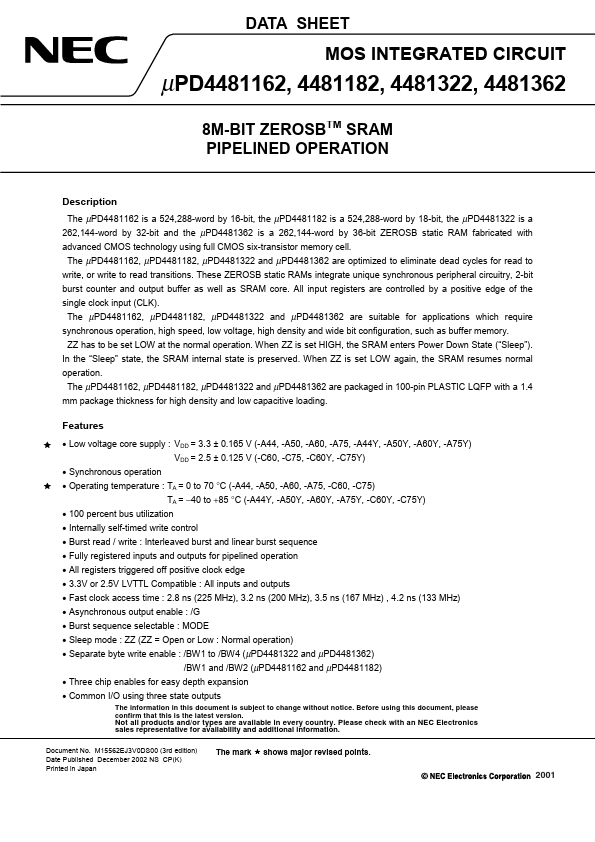

The µPD4481162 is a 524,288-word by 16-bit, the µPD4481182 is a 524,288-word by 18-bit, the µPD4481322 is a 262,144-word by 32-bit and the µPD4481362 is a 262,144-word by 36-bit ZEROSB static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell. The µPD4481162, µPD4481182, µPD4481322 and µPD4481362 are optimized to eliminate dead cycles for read to write, or write to read transitions.

Key Features

- Synchronous operation

- 100 percent bus utilization

- Internally self-timed write control

- Burst read / write : Interleaved burst and linear burst sequence

- Fully registered inputs and outputs for pipelined operation

- All registers triggered off positive clock edge