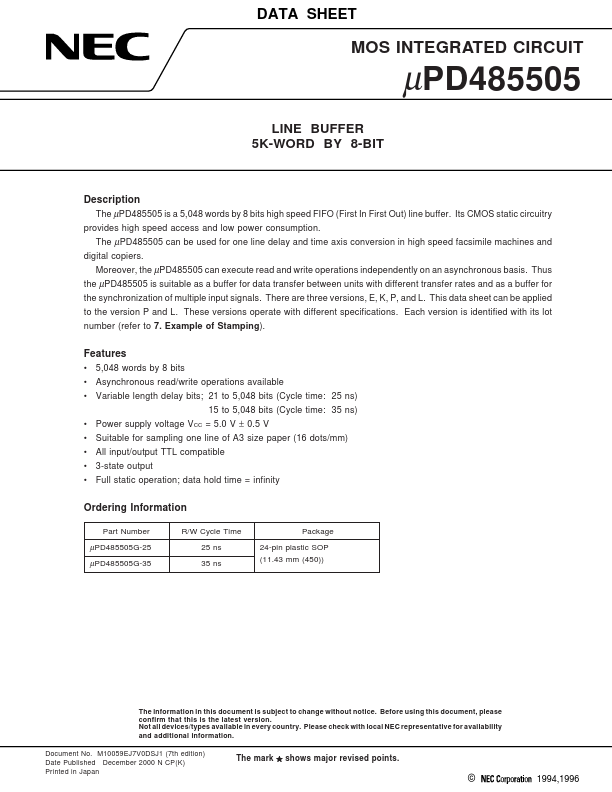

UPD485505

Overview

The µPD485505 is a 5,048 words by 8 bits high speed FIFO (First In First Out) line buffer. Its CMOS static circuitry provides high speed access and low power consumption.

- 5,048 words by 8 bits

- Asynchronous read/write operations available

- Variable length delay bits; 21 to 5,048 bits (Cycle time: 25 ns) 15 to 5,048 bits (Cycle time: 35 ns)

- Power supply voltage VCC = 5.0 V ± 0.5 V

- Suitable for sampling one line of A3 size paper (16 dots/mm)

- All input/output TTL compatible

- 3-state output

- Full static operation; data hold time = infinity