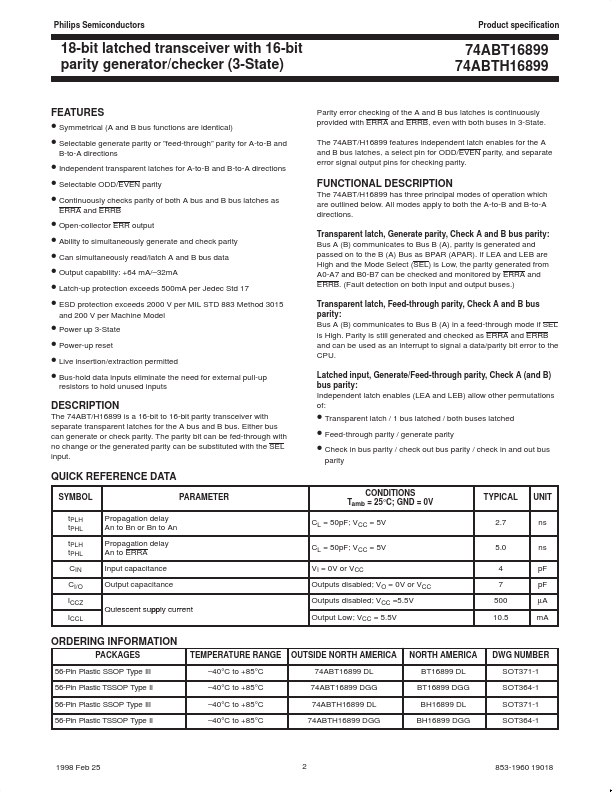

74ABT16899 Description

The 74ABT/H16899 has three principal modes of operation which are outlined below. All modes apply to both the A-to-B and B-to-A directions. Transparent latch, Generate parity, Check A and B bus parity:.

74ABT16899 Key Features

- Symmetrical (A and B bus functions are identical)

- Selectable generate parity or ”feed-through” parity for A-to-B and

- Independent transparent latches for A-to-B and B-to-A directions

- Selectable ODD/EVEN parity

- Continuously checks parity of both A bus and B bus latches as

- Open-collector ERR output

- Ability to simultaneously generate and check parity

- Can simultaneously read/latch A and B bus data

- Output capability: +64 mA/-32mA

- Latch-up protection exceeds 500mA per Jedec Std 17