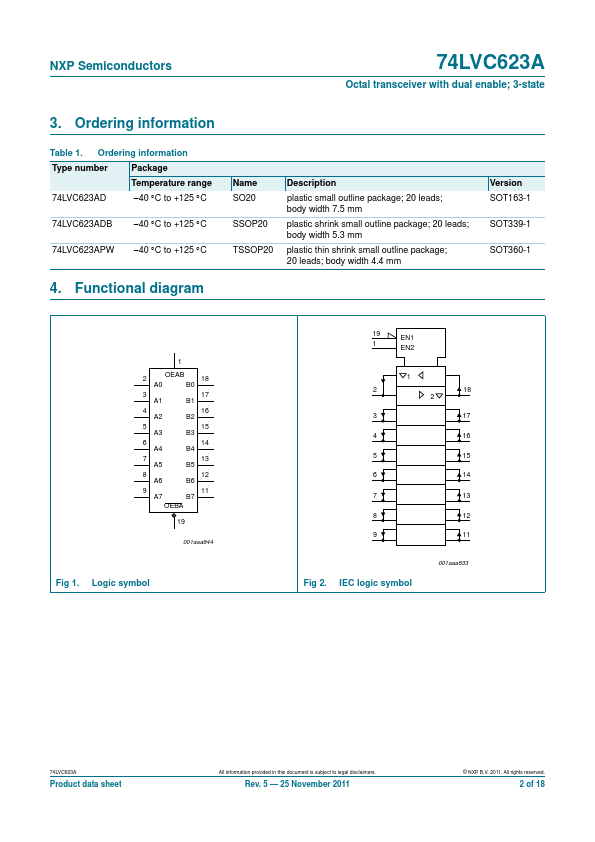

74LVC623A Overview

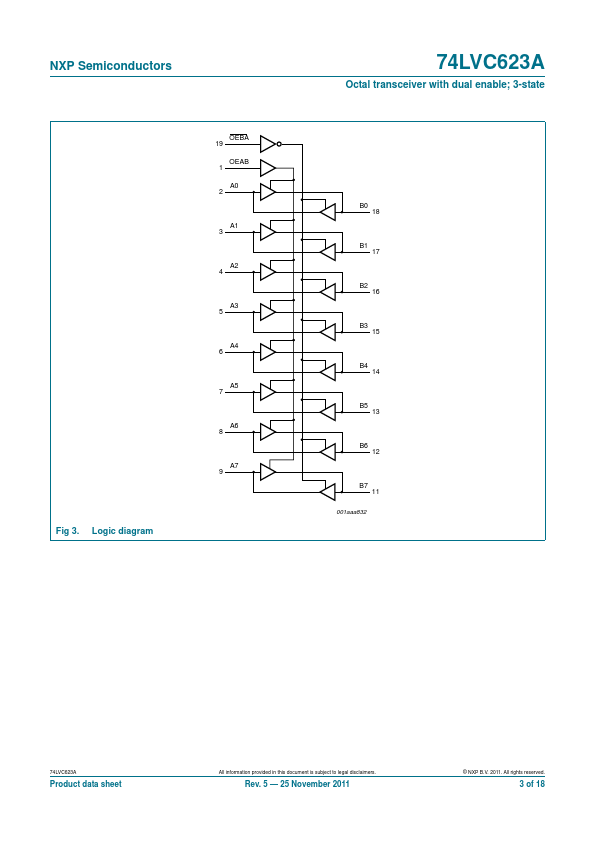

The 74LVC623A is an octal transceiver featuring non-inverting 3-state bus patible outputs in both send and receive directions. This octal bus transceiver is designed for asynchronous two-way munication between data buses. The control function implementation allows maximum flexibility in timing.

74LVC623A Applications

- 5 V tolerant inputs and outputs for interfacing with 5 V logic

- Wide supply voltage range from 1.2 V to 3.6 V