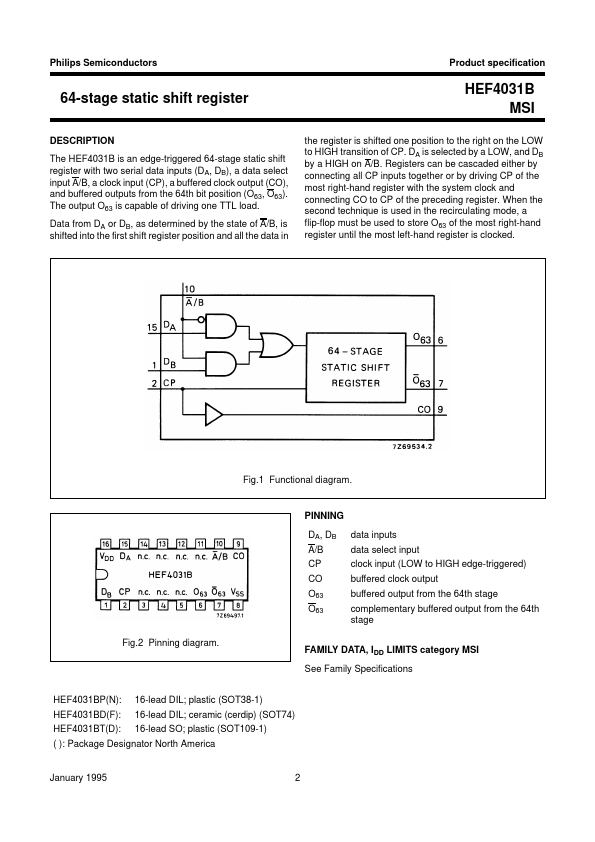

HEF4031B Description

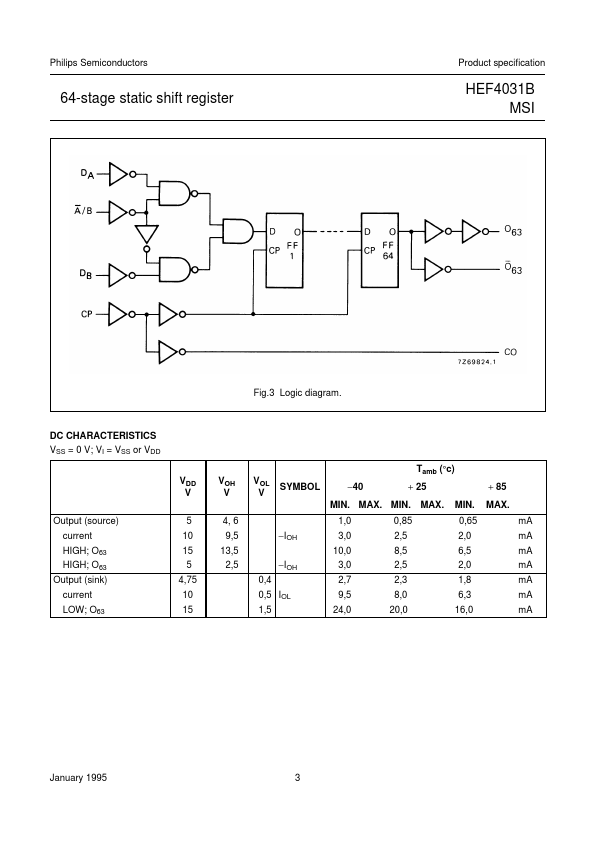

The HEF4031B is an edge-triggered 64-stage static shift register with two serial data inputs (DA, DB), a data select input A/B, a clock input (CP), a buffered clock output (CO), and buffered outputs from the 64th bit position (O63, O63). The output O63 is capable of driving one TTL load. Data from DA or DB, as determined by the state of A/B, is shifted into the first shift register position and all the data in...