PHB65N06LT

PHB65N06LT is Transistor manufactured by NXP Semiconductors.

Philips Semiconductors

Product specification

Trench MOS™ transistor Logic level FET

GENERAL DESCRIPTION

N-channel enhancement mode logic level field-effect power transistor in a plastic envelope suitable for surface mounting. Using ’trench’ technology the device Features very low on-state resistance and has integral zener diodes giving ESD protection up to 2k V. It is intended for use in DC-DC converters and general purpose switching applications.

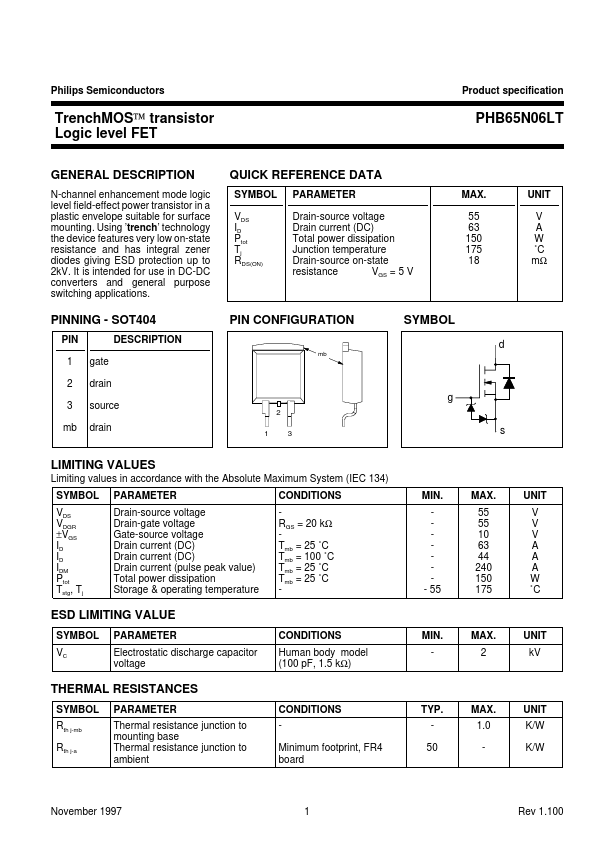

QUICK REFERENCE DATA

SYMBOL VDS ID Ptot Tj RDS(ON) PARAMETER Drain-source voltage Drain current (DC) Total power dissipation Junction temperature Drain-source on-state resistance VGS = 5 V MAX. 55 63 150 175 18 UNIT V A W ˚C mΩ

PINNING

- SOT404

PIN 1 2 3 mb gate drain source drain DESCRIPTION

PIN CONFIGURATION mb

SYMBOL d g

2 1 3 s

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134) SYMBOL VDS VDGR ±VGS ID ID IDM Ptot Tstg, Tj PARAMETER Drain-source voltage Drain-gate voltage Gate-source voltage Drain current (DC) Drain current (DC) Drain current (pulse peak value) Total power dissipation Storage & operating temperature CONDITIONS RGS = 20 kΩ Tmb = 25 ˚C Tmb = 100 ˚C Tmb = 25 ˚C Tmb = 25 ˚C MIN.

- 55 MAX. 55 55 10 63 44 240 150 175 UNIT V V V A A A W ˚C

ESD LIMITING VALUE

SYMBOL VC PARAMETER Electrostatic discharge capacitor voltage CONDITIONS Human body model (100 p F, 1.5 kΩ) MIN. MAX. 2 UNIT k V

THERMAL RESISTANCES

SYMBOL Rth j-mb Rth j-a PARAMETER Thermal resistance junction to mounting base Thermal resistance junction to ambient CONDITIONS Minimum footprint, FR4 board TYP. 50 MAX. 1.0 UNIT K/W K/W

November 1997

Rev 1.100

Philips Semiconductors

Product specification

Trench MOS™ transistor Logic level FET

STATIC CHARACTERISTICS

Tj= 25˚C unless otherwise specified SYMBOL V(BR)DSS VGS(TO) IDSS IGSS ±V(BR)GSS RDS(ON) PARAMETER Drain-source breakdown voltage Gate threshold voltage Zero gate voltage drain current Gate source leakage current Gate-source...