PLS100 Overview

Key Specifications

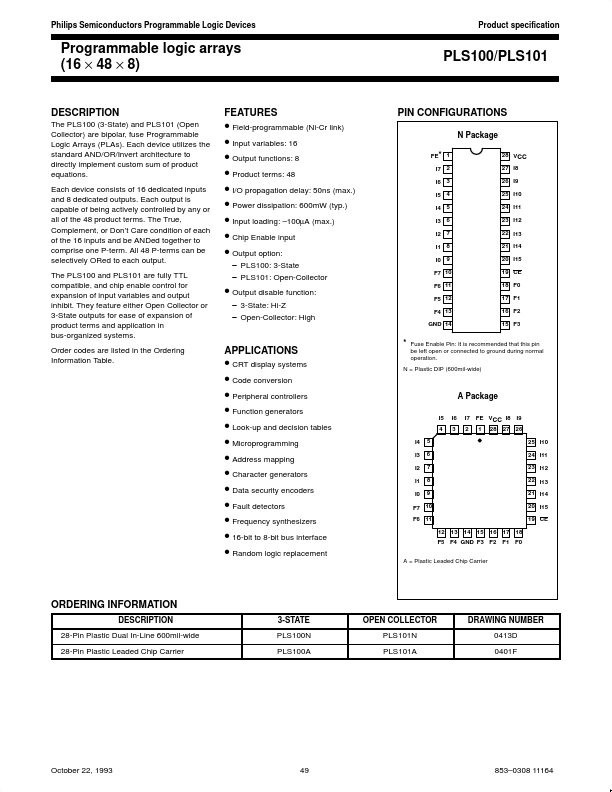

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 5.25 V

Min Voltage (typical range): 4.75 V

Description

The PLS100 (3-State) and PLS101 (Open Collector) are bipolar, fuse Programmable Logic Arrays (PLAs). Each device utilizes the standard AND/OR/Invert architecture to directly implement custom sum of product equations.

Key Features

- Field-programmable (Ni-Cr link)

- Input variables: 16

- Output functions: 8

- Product terms: 48

- I/O propagation delay: 50ns (max.)