PMN55LN Overview

Key Specifications

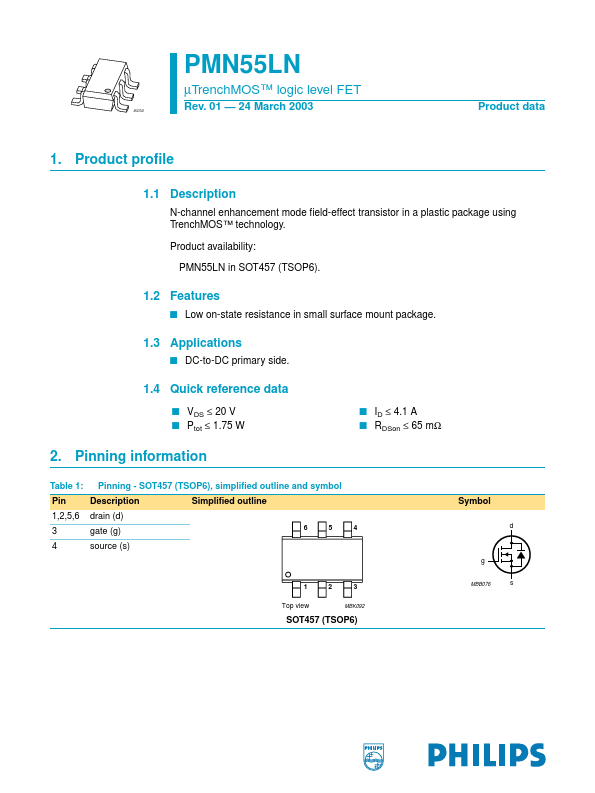

Package: TSOP

Mount Type: Surface Mount

Pins: 6

Max Operating Temp: 150 °C

Key Features

- s Low on-state resistance in small surface mount package

- 1.3 Applications s DC-to-DC primary side

- 1.4 Quick reference data s VDS ≤ 20 V s Ptot ≤ 1.75 W s ID ≤ 4.1 A s RDSon ≤ 65 mΩ