S32R372

S32R372 is 32-bit CPU manufactured by NXP Semiconductors.

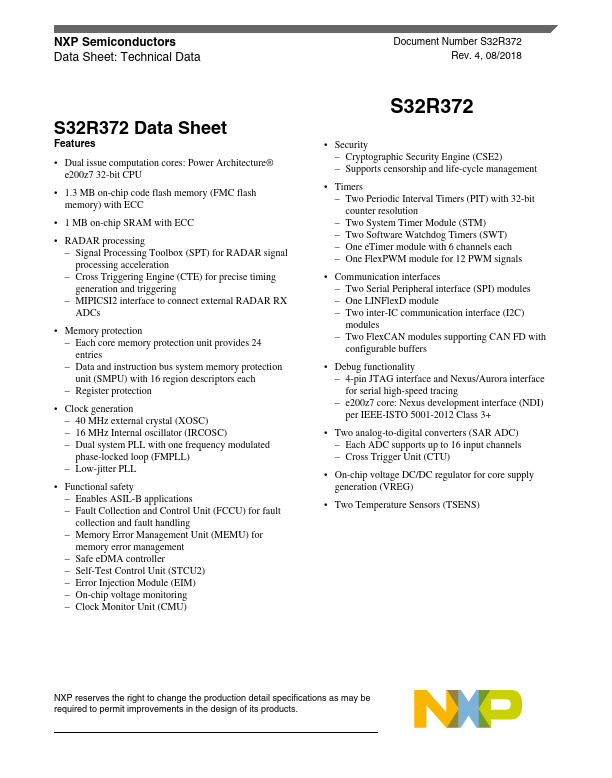

NXP Semiconductors Data Sheet: Technical Data

S32R372 Data Sheet

Features

- Dual issue putation cores: Power Architecture® e200z7 32-bit CPU

- 1.3 MB on-chip code flash memory (FMC flash memory) with ECC

- 1 MB on-chip SRAM with ECC

- RADAR processing

- Signal Processing Toolbox (SPT) for RADAR signal processing acceleration

- Cross Triggering Engine (CTE) for precise timing generation and triggering

- MIPICSI2 interface to connect external RADAR RX ADCs

- Memory protection

- Each core memory protection unit provides 24 entries

- Data and instruction bus system memory protection unit (SMPU) with 16 region descriptors each

- Register protection

- Clock generation

- 40 MHz external crystal (XOSC)

- 16 MHz Internal oscillator (IRCOSC)

- Dual system PLL with one frequency modulated phase-locked loop (FMPLL)

- Low-jitter PLL

- Functional safety

- Enables ASIL-B applications

- Fault Collection and Control Unit (FCCU) for fault collection and fault handling

- Memory Error Management Unit (MEMU) for memory error management

- Safe e DMA controller

- Self-Test Control Unit (STCU2)

- Error Injection Module (EIM)

- On-chip voltage monitoring

- Clock Monitor Unit (CMU)

Document Number S32R372 Rev. 4, 08/2018

-...