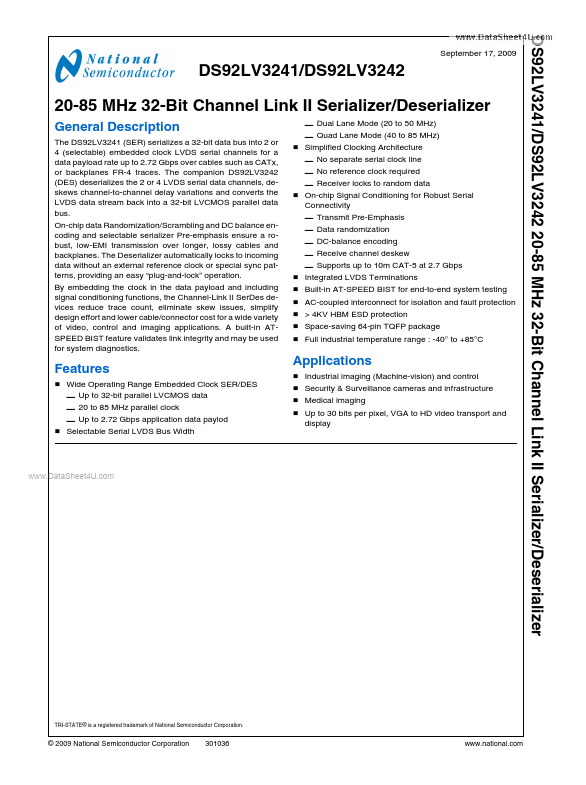

DS92LV3241

Description

The DS92LV3241 (SER) serializes a 32-bit data bus into 2 or 4 (selectable) embedded clock LVDS serial channels for a data payload rate up to 2.72 Gbps over cables such as CATx, or backplanes FR-4 traces.

Key Features

- Wide Operating Range Embedded Clock SER/DES

- Selectable Serial LVDS Bus Width

Applications

- Industrial imaging (Machine-vision) and control Security & Surveillance cameras and infrastructure Medical imaging Up to 30 bits per pixel, VGA to HD video transport and display