CD40175BM

Description

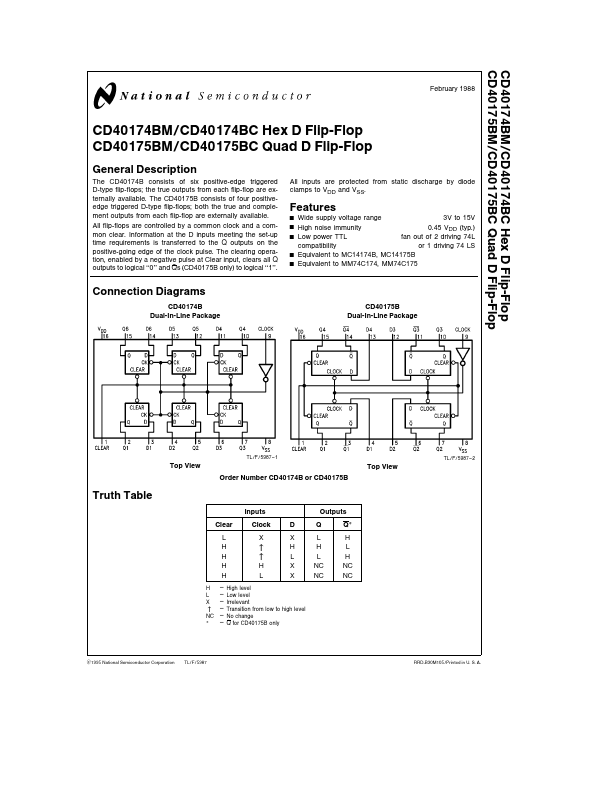

The CD40174B consists of six positive-edge triggered D-type flip-flops the true outputs from each flip-flop are externally available The CD40175B consists of four positiveedge triggered D-type flip-flops both the true and plement outputs from each flip-flop are externally available All flip-flops are controlled by a mon clock and a mon clear Information at the D inputs meeting the set-up time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse The clearing operation enabled by a negative pulse at Clear input clears all Q outputs to logical ‘‘0’’ and Qs (CD40175B only) to logical ‘‘1’’ All inputs are protected from static discharge by diode clamps to VDD and VSS.