DP8459

DP8459 is All-Code Data Synchronizer manufactured by National Semiconductor.

Description

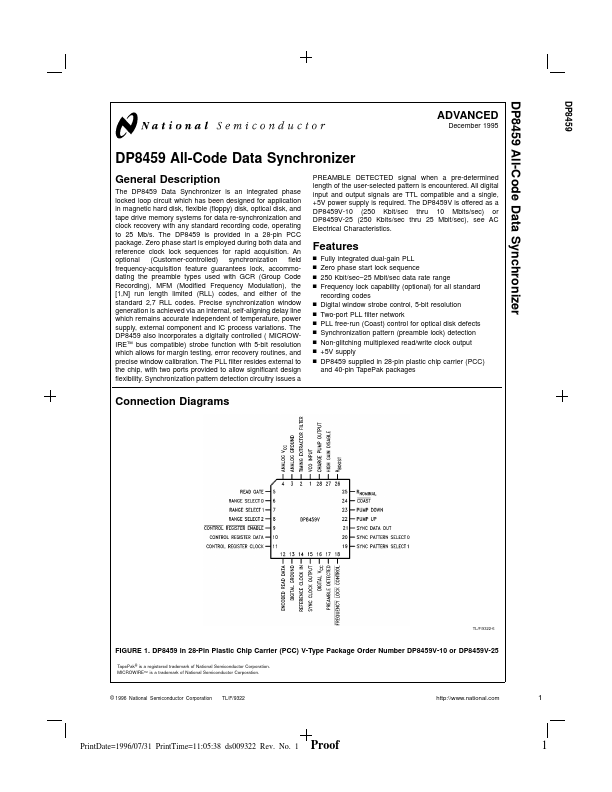

The DP8459 Data Synchronizer is an integrated phase locked loop circuit which has been designed for application in magnetic hard disk, flexible (floppy) disk, optical disk, and tape drive memory systems for data re-synchronization and clock recovery with any standard recording code, operating to 25 Mb/s. The DP8459 is provided in a 28-pin PCC package. Zero phase start is employed during both data and reference clock lock sequences for rapid acquisition. An optional (Customer-controlled) synchronization field frequency-acquisition feature guarantees lock, acmodating the preamble types used with GCR (Group Code Recording), MFM (Modified Frequency Modulation), the [1,N] run length limited (RLL) codes, and either of the standard 2,7 RLL codes. Precise synchronization window generation is achieved via an internal, self-aligning delay line which remains accurate independent of temperature, power supply, external ponent and IC process variations. The DP8459 also incorporates a digitally controlled ( MICROWIRE™ bus patible) strobe function with 5-bit resolution which allows for margin testing, error recovery routines, and precise window calibration. The PLL filter resides external to the chip, with two ports provided to allow significant design flexibility. Synchronization pattern detection circuitry issues a PREAMBLE DETECTED signal when a pre-determined length of the user-selected pattern is encountered. All digital input and output signals are TTL patible and a single, +5V power supply is required. The DP8459V is offered as a DP8459V-10 (250 Kbit/sec thru 10 Mbits/sec) or DP8459V-25 (250 Kbits/sec thru 25 Mbit/sec), see AC Electrical Characteristics.

Features n n n n n n n n n n n Fully integrated dual-gain PLL Zero phase start lock sequence 250 Kbit/sec- 25 Mbit/sec data rate range Frequency lock capability (optional) for all standard recording codes Digital window strobe control, 5-bit resolution Two-port PLL filter network PLL free-run (Coast) control for optical...