DS90C363A

DS90C363A is +3.3V Programmable LVDS Transmitter manufactured by National Semiconductor.

DS90C363A/DS90CF363A +3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD) Link-65 MHz, +3.3V LVDS Transmitter 18-Bit Flat Panel Display (FPD)Link-65 MHz

June 1998

DS90C363A/DS90CF363A +3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD) Link-65 MHz +3.3V LVDS Transmitter 18-Bit Flat Panel Display (FPD) Link-65 MHz

General Description

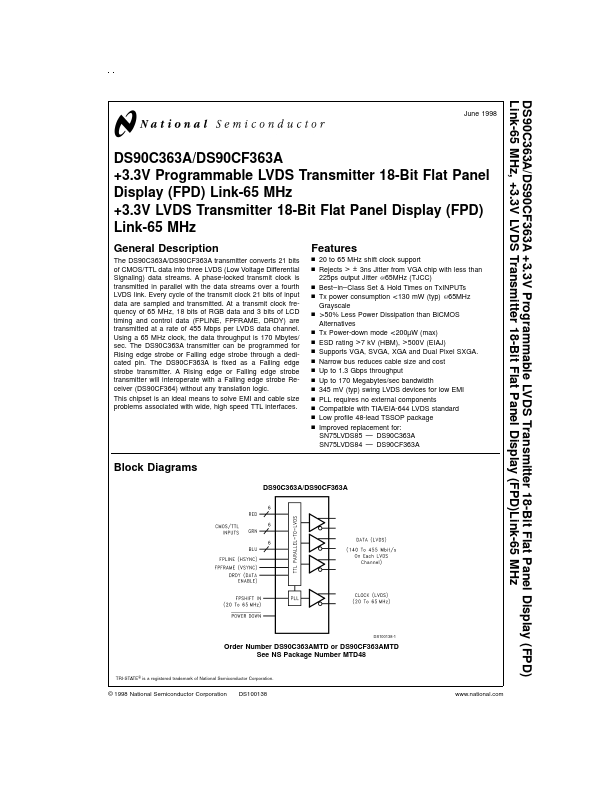

The DS90C363A/DS90CF363A transmitter converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. Every cycle of the transmit clock 21 bits of input data are sampled and transmitted. At a transmit clock frequency of 65 MHz, 18 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 455 Mbps per LVDS data channel. Using a 65 MHz clock, the data throughput is 170 Mbytes/ sec. The DS90C363A transmitter can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin. The DS90CF363A is fixed as a Falling edge strobe transmitter. A Rising edge or Falling edge strobe transmitter will interoperate with a Falling edge strobe Receiver (DS90CF364) without any translation logic. This chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

Features n 20 to 65 MHz shift clock support n Rejects > ± 3ns Jitter from VGA chip with less than 225ps output Jitter @65MHz (TJCC) n Best- in- Class Set & Hold Times on Tx INPUTs n Tx power consumption < 130 m W (typ) @65MHz Grayscale n > 50% Less Power Dissipation than Bi CMOS Alternatives n Tx Power-down mode < 200µW (max) n ESD rating > 7 k V (HBM), > 500V (EIAJ) n Supports VGA, SVGA, XGA and Dual Pixel SXGA. n Narrow bus reduces cable size and cost n Up to 1.3 Gbps throughput n Up to 170 Megabytes/sec bandwidth n 345 m V (typ) swing LVDS devices for low EMI n PLL requires no external ponents n patible...