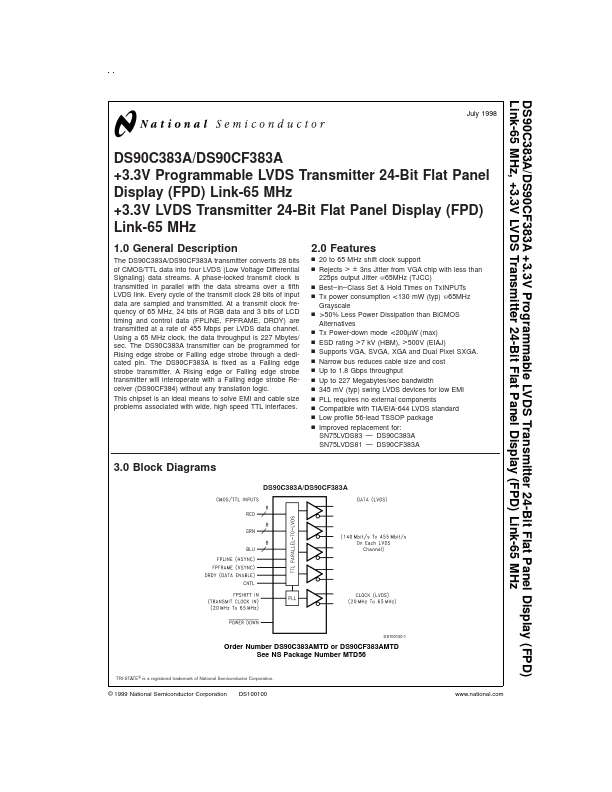

DS90C383A Overview

Key Features

- Rejects > ± 3ns Jitter from VGA chip with less than 225ps output Jitter @65MHz (TJCC)

- Best–in–Class Set & Hold Times on TxINPUTs

- Tx power consumption < 130 mW (typ) @65MHz Grayscale n > 50% Less Power Dissipation than BiCMOS Alternatives

- Tx Power-down mode < 200µW (max)

- ESD rating > 7 kV (HBM), > 500V (EIAJ)

- Supports VGA, SVGA, XGA and Dual Pixel SXGA

- Narrow bus reduces cable size and cost

- Up to 1.8 Gbps throughput

- Up to 227 Megabytes/sec bandwidth n 345 mV (typ) swing LVDS devices for low EMI

- PLL requires no external components n