74F273

74F273 is Octal D Flip-Flop manufactured by National Semiconductor.

Description

The ’F273 has eight edge-triggered D-type flip-flops with individual D inputs and Q outputs The mon buffered Clock (CP) and Master Reset (MR) inputs load and reset (clear) all flip-flops simultaneously The register is fully edge-triggered The state of each D input one setup time before the LOW-to-HIGH clock transition is transferred to the corresponding flip-flop’s Q output All outputs will be forced LOW independently of Clock or Data inputs by a LOW voltage level on the MR input The device is useful for applications where the true output only is required and the Clock and Master Reset are mon to all storage elements

Features

Y Y Y Y Y Y Y Y

Ideal buffer for MOS microprocessor or memory Eight edge-triggered D flip-flops Buffered mon clock Buffered asynchronous Master Reset See ’F377 for clock enable version See ’F373 for transparent latch version See ’F374 for TRI-STATE version Guaranteed 4000V minimum ESD protection mercial 74F273PC

Military

Package Number N20A

Package Description

20-Lead (0 300 Wide) Molded Dual-In-Line 20-Lead Ceramic Dual-In-Line 20-Lead (0 300 Wide) Molded Small Outline JEDEC 20-Lead (0 300 Wide) Molded Small Outline EIAJ 20-Lead Cerpack 20-Lead Ceramic Leadless Chip Carrier Type C

54F273DM (Note 2) 74F273SC (Note 1) 74F273SJ (Note 1) 54F273FM (Note 2) 54F273LM (Note 2)

J20A M20B M20D W20A E20A

Note 1 Devices also available in 13 reel Use suffix e SCX and SJX Note 2 Military grade device with environmental and burn-in processing Use suffix e DMQB FMQB and LMQB

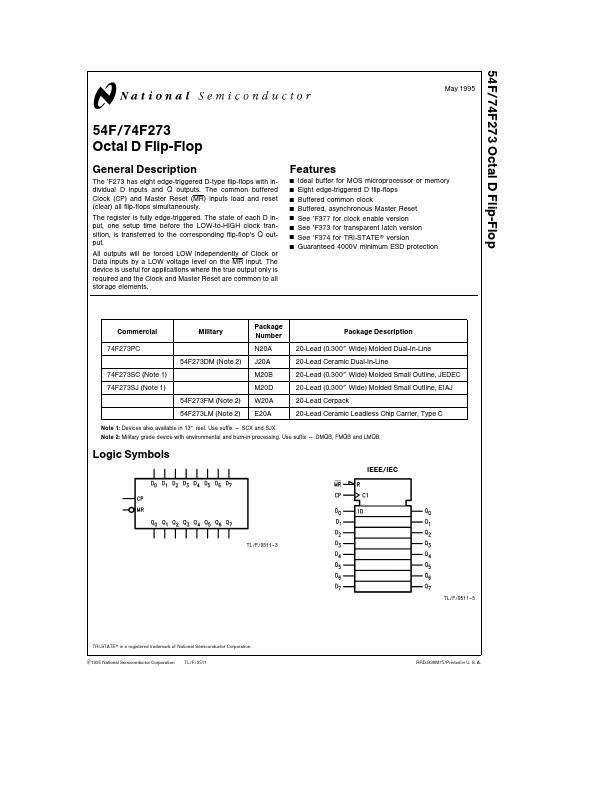

Logic Symbols

IEEE IEC

TL F 9511

- 3

TL F 9511

- 5

TRI-STATE is a registered trademark of National Semiconductor Corporation C1995 National Semiconductor Corporation

TL F 9511

RRD-B30M75 Printed in U S A

Connection Diagrams

Pin Assignment for DIP SOIC and Flatpak Pin Assignment for LCC

TL F 9511

- 2 TL F 9511- 1

Unit Loading Fan Out

54F 74F Pin Names Description

UL Input IIH IIL HIGH LOW Output IOH IOL 10 10 10 10 10 10 50 33 3 20 m A b0 6 m A 20 m A b0 6 m A 20...