SCAN50C400

SCAN50C400 is 1.25/2.5/5.0 GBPS Quad Multi-rate Backplane Transceiver manufactured by National Semiconductor.

Description

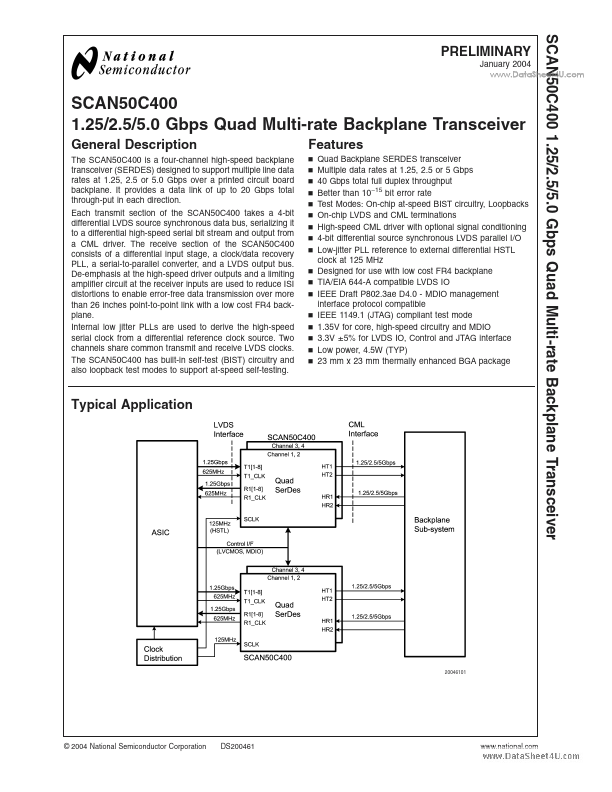

The SCAN50C400 is a four-channel high-speed backplane transceiver (SERDES) designed to support multiple line data rates at 1.25, 2.5 or 5.0 Gbps over a printed circuit board backplane. It provides a data link of up to 20 Gbps total through-put in each direction. Each transmit section of the SCAN50C400 takes a 4-bit differential LVDS source synchronous data bus, serializing it to a differential high-speed serial bit stream and output from a CML driver. The receive section of the SCAN50C400 consists of a differential input stage, a clock/data recovery PLL, a serial-to-parallel converter, and a LVDS output bus. De-emphasis at the high-speed driver outputs and a limiting amplifier circuit at the receiver inputs are used to reduce ISI distortions to enable error-free data transmission over more than 26 inches point-to-point link with a low cost FR4 backplane. Internal low jitter PLLs are used to derive the high-speed serial clock from a differential reference clock source. Two channels share mon transmit and receive LVDS clocks. The SCAN50C400 has built-in self-test (BIST) circuitry and also loopback test modes to support at-speed self-testing.

Features n n n n n n n n n n n n n n n n n Quad Backplane SERDES transceiver Multiple data rates at 1.25, 2.5 or 5 Gbps 40 Gbps total full duplex throughput Better than 10- 15 bit error rate Test Modes: On-chip at-speed BIST circuitry, Loopbacks On-chip LVDS and CML terminations High-speed CML driver with optional signal conditioning 4-bit differential source synchronous LVDS parallel I/O Low-jitter PLL reference to external differential HSTL clock at 125 MHz Designed for use with low cost FR4 backplane TIA/EIA 644-A patible LVDS IO IEEE Draft P802.3ae D4.0

- MDIO management interface protocol patible IEEE 1149.1 (JTAG) pliant test mode 1.35V for core, high-speed circuitry and MDIO 3.3V ± 5% for LVDS IO, Control and JTAG interface Low power, 4.5W (TYP) 23 mm x 23 mm thermally enhanced BGA package

Typical...