SM8211M

OVERVIEW

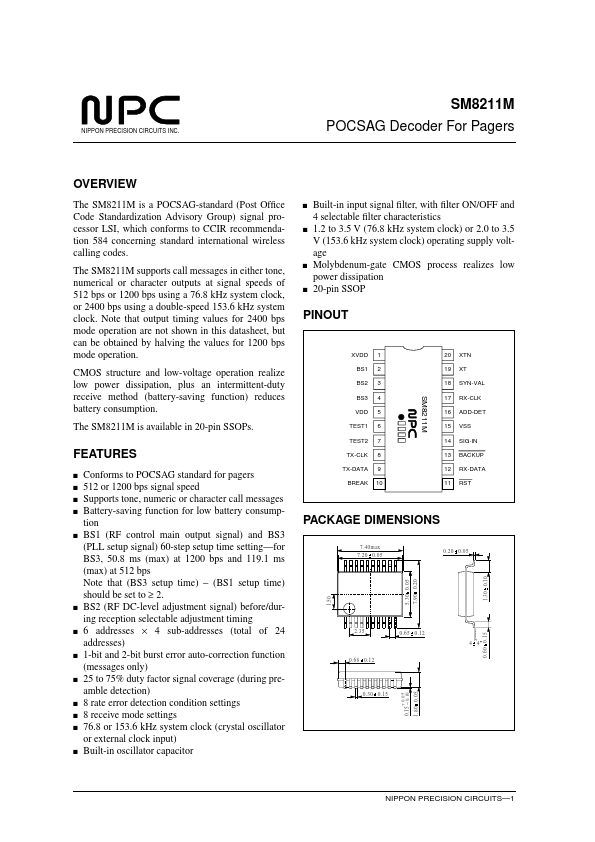

The SM8211M is a POCSAG-standard (Post Office Code Standardization Advisory Group) signal processor LSI, which conforms to CCIR remendation 584 concerning standard international wireless calling codes. The SM8211M supports call messages in either tone, numerical or character outputs at signal speeds of 512 bps or 1200 bps using a 76.8 k Hz system clock, or 2400 bps using a double-speed 153.6 k Hz system clock. Note that output timing values for 2400 bps mode operation are not shown in this datasheet, but can be obtained by halving the values for 1200 bps mode operation. CMOS structure and low-voltage operation realize low power dissipation, plus an intermittent-duty receive method (battery-saving function) reduces battery consumption. The SM8211M is available in 20-pin SSOPs. s s s s

Built-in input signal filter, with filter ON/OFF and 4 selectable filter characteristics 1.2 to 3.5 V (76.8 k Hz system clock) or 2.0 to 3.5 V (153.6 k Hz system clock) operating supply voltage...