SM8212B

OVERVIEW

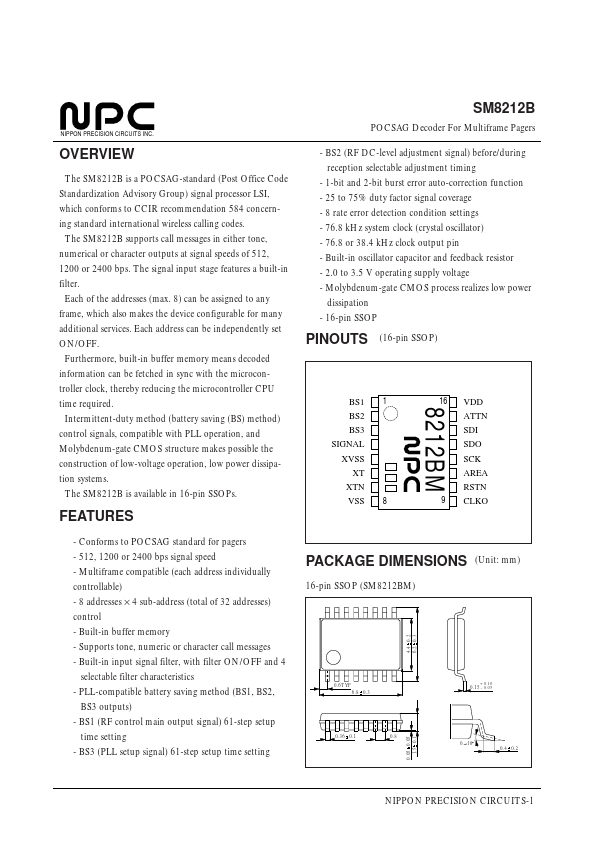

The SM8212B is a POCSAG-standard (Post Office Code Standardization Advisory Group) signal processor LSI, which conforms to CCIR remendation 584 concerning standard international wireless calling codes. The SM8212B supports call messages in either tone, numerical or character outputs at signal speeds of 512, 1200 or 2400 bps. The signal input stage features a built-in filter. Each of the addresses (max. 8) can be assigned to any frame, which also makes the device configurable for many additional services. Each address can be independently set ON/OFF. Furthermore, built-in buffer memory means decoded information can be fetched in sync with the microcontroller clock, thereby reducing the microcontroller CPU time required. Intermittent-duty method (battery saving (BS) method) control signals, patible with PLL operation, and Molybdenum-gate CMOS structure makes possible the construction of low-voltage operation, low power dissipation systems. The SM8212B is available in 16-pin...