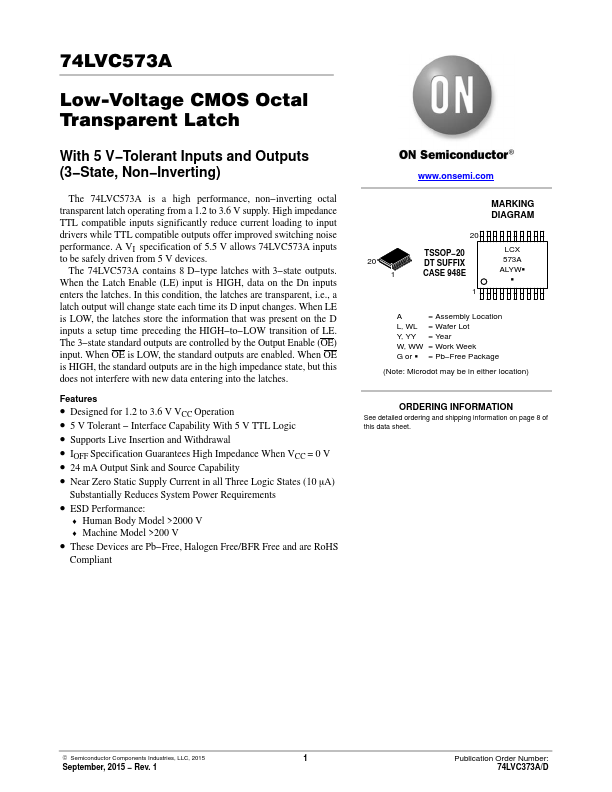

74LVC573A

Overview

- Designed for 1.2 to 3.6 V VCC Operation

- 5 V Tolerant - Interface Capability With 5 V TTL Logic

- Supports Live Insertion and Withdrawal

- IOFF Specification Guarantees High Impedance When VCC = 0 V

- 24 mA Output Sink and Source Capability

- Near Zero Static Supply Current in all Three Logic States (10 mA) Substantially Reduces System Power Requirements

- ESD Performance:

- Human Body Model >2000 V

- Machine Model >200 V

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant 20 1