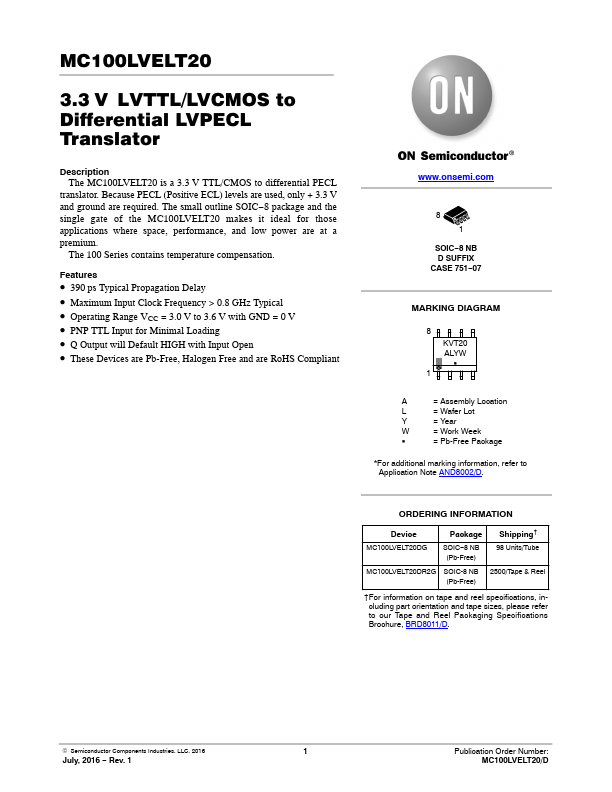

MC100LVELT20

Overview

- 390 ps Typical Propagation Delay

- Maximum Input Clock Frequency > 0.8 GHz Typical

- Operating Range VCC = 3.0 V to 3.6 V with GND = 0 V

- PNP TTL Input for Minimal Loading

- Q Output will Default HIGH with Input Open

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant 8 1