MC74HC390A Overview

Key Specifications

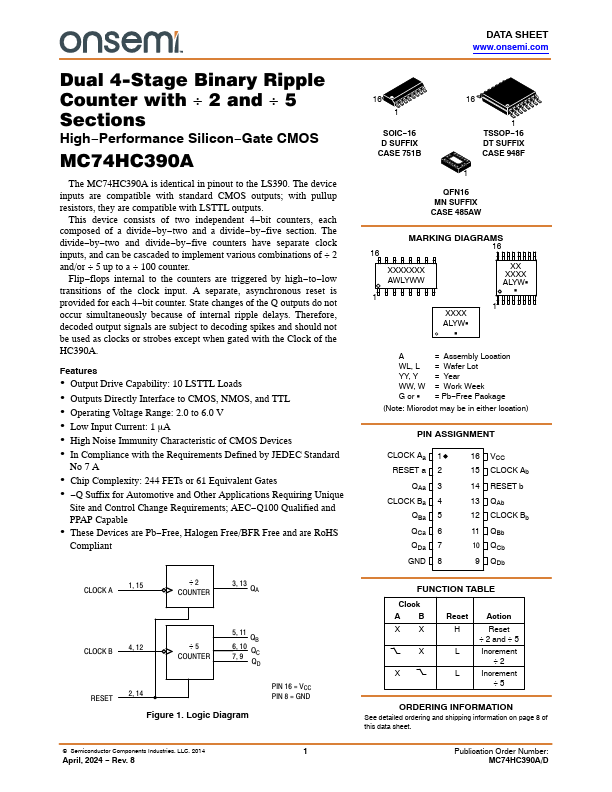

Package: SOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 5 V

Key Features

- Output Drive Capability: 10 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 to 6.0 V

- Low Input Current: 1 mA

- High Noise Immunity Characteristic of CMOS Devices