Datasheet Summary

2.5V/3.3V 2:1:20

Differential HSTL/ECL/PECL

Clock Driver

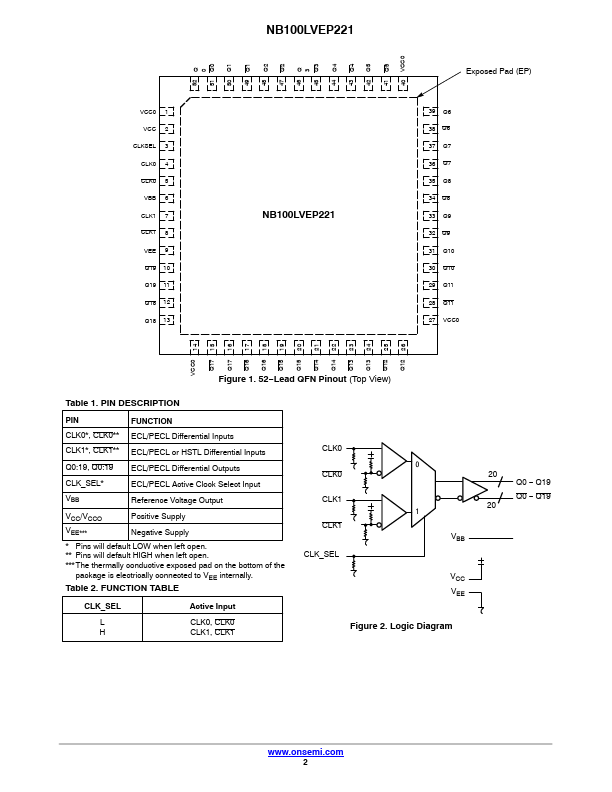

Description The NB100LVEP221 is a low skew 2:1:20 differential clock driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The two clock inputs are differential ECL/PECL; CLK1/CLK1 can also receive HSTL signal levels. The LVPECL input signals can be either differential configuration or single- ended (if the VBB output is used).

The LVEP221 specifically guarantees low output- to- output skew. Optimal design, layout, and processing minimize skew within a device and from device to device.

To ensure tightest skew, both sides of differential outputs should be terminated...