Datasheet Summary

NB100LVEP224 2.5V/3.3V 1:24 Differential ECL/PECL Clock Driver with Clock Select and Output Enable

Description http://onsemi. MARKING DIAGRAM-

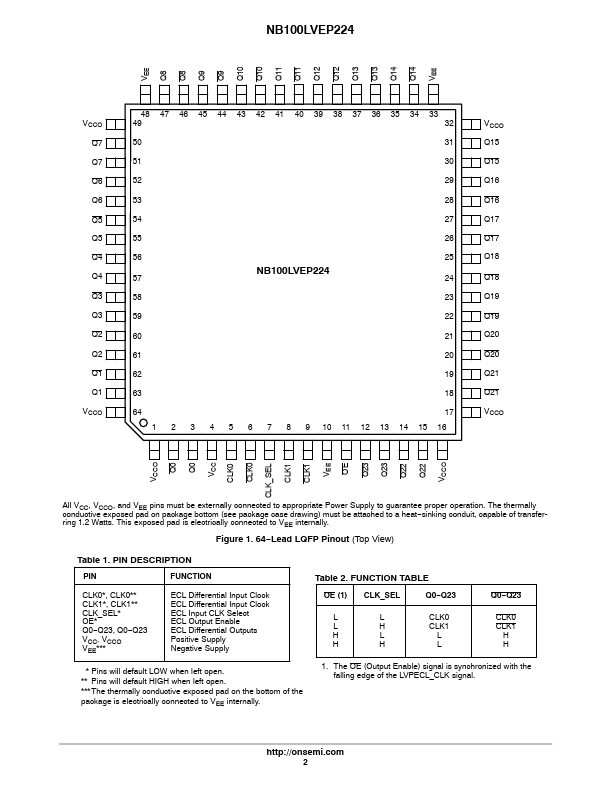

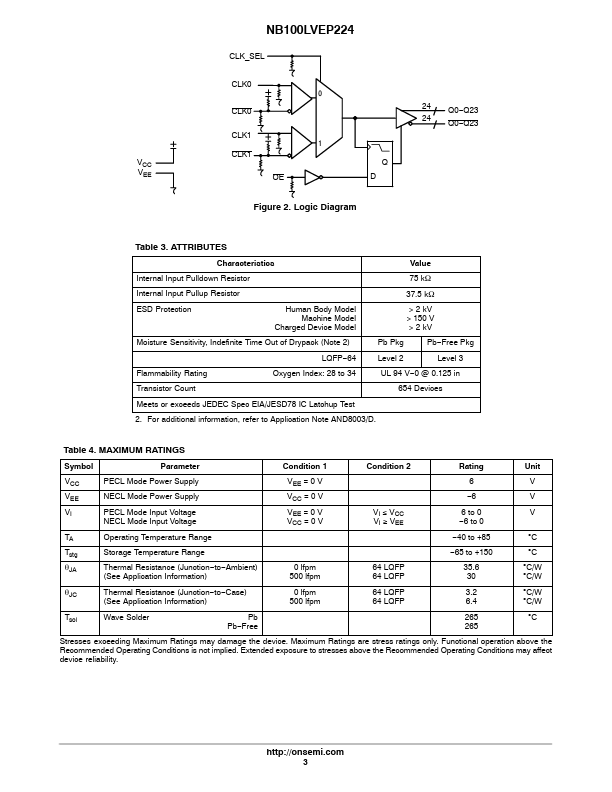

The NB100LVEP224 is a low skew 1- to- 24 differential clock driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The part is designed for use in low voltage applications which require a large number of outputs to drive precisely aligned low skew signals to their destination. The two clock inputs are differential ECL/PECL and they are selected by the CLK_SEL pin. To avoid generation of a runt clock pulse when the device is enabled/disabled, the Output Enable (OE) is synchronous ensuring the...