NB6L239 Description

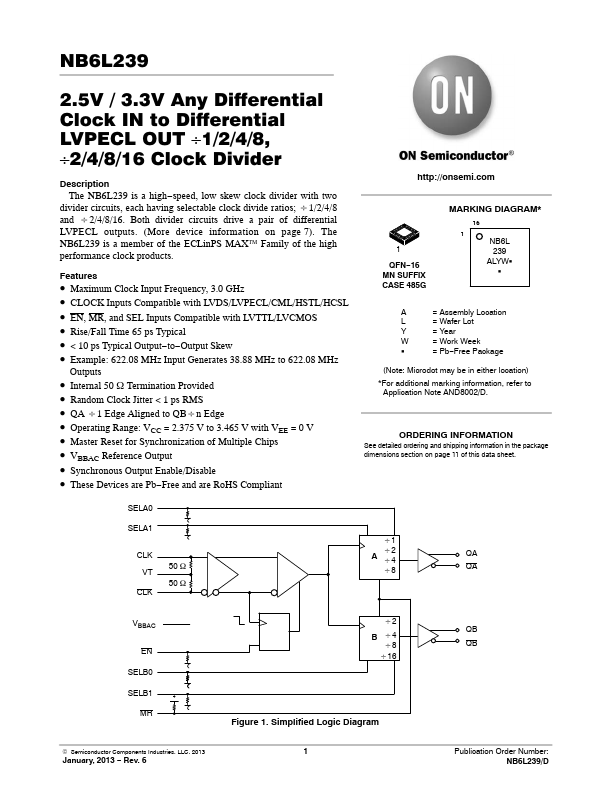

The NB6L239 is a high−speed, low skew clock divider with two divider circuits, each having selectable clock divide ratios; Both divider circuits drive a pair of differential LVPECL outputs. (More device information on page 7).

NB6L239 Key Features

- Maximum Clock Input Frequency, 3.0 GHz

- CLOCK Inputs patible with LVDS/LVPECL/CML/HSTL/HCSL

- EN, MR, and SEL Inputs patible with LVTTL/LVCMOS

- Rise/Fall Time 65 ps Typical

- < 10 ps Typical Output-to-Output Skew

- Example: 622.08 MHz Input Generates 38.88 MHz to 622.08 MHz

- Internal 50 W Termination Provided

- Random Clock Jitter < 1 ps RMS

- QA B1 Edge Aligned to QBBn Edge

- Operating Range: VCC = 2.375 V to 3.465 V with VEE = 0 V